# 芯动力——硬件加速设计方法

第五章 静态时序分析(1)

邸志雄@西南交通大学 zxdi@home.swjtu.edu.cn

## 0 Nanometer Designs. Springer, 2009. Chapter-8.

. Bhasker Rakesh Chadha

Description Springer

© 2009

A Practical Approach

Authors: Bhasker, J., Chadha, Rakesh

Rakesh ChadhaJ. Bhasker. Static Timing Analysis for

# Static Timing Analysis for Nanometer Designs

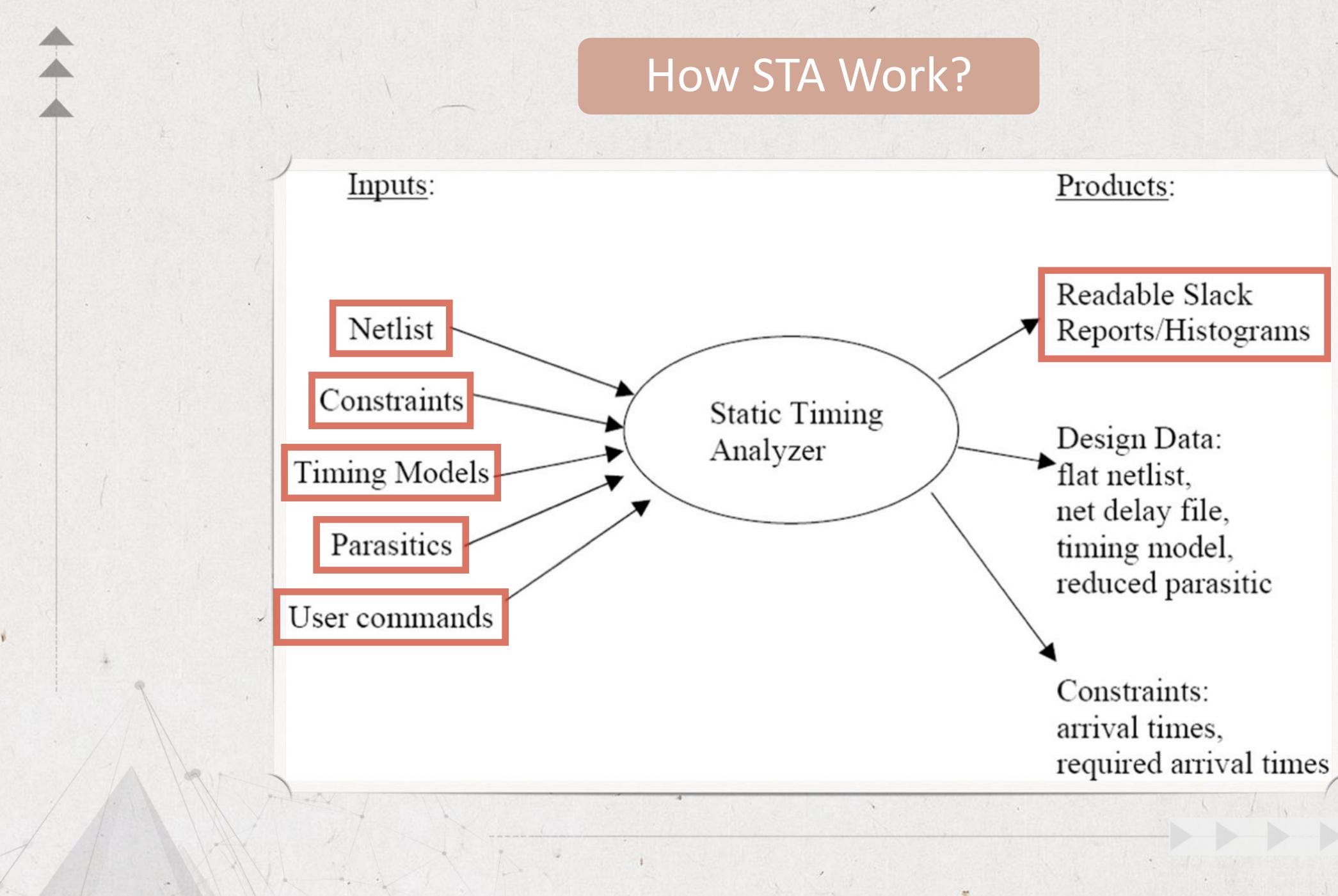

# What Is Static Timing Analysis?

0 meets time constraints without beversimulation imulate: Proper circuit functionality is not checked Vector generation NOT required

Static Timing Analysis is a method for determining if a circuit

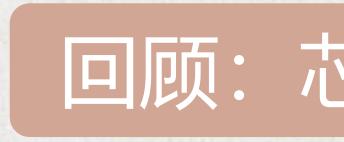

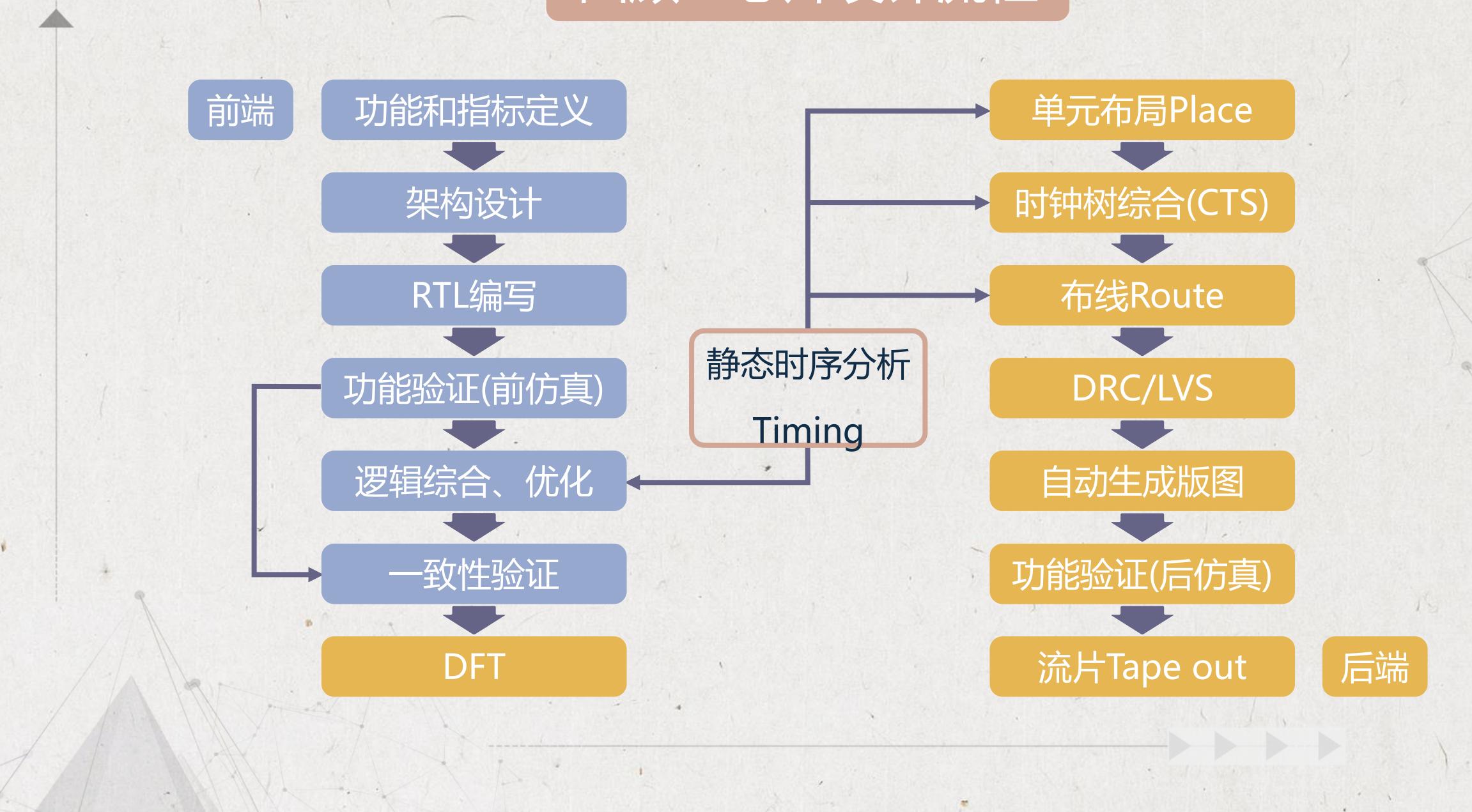

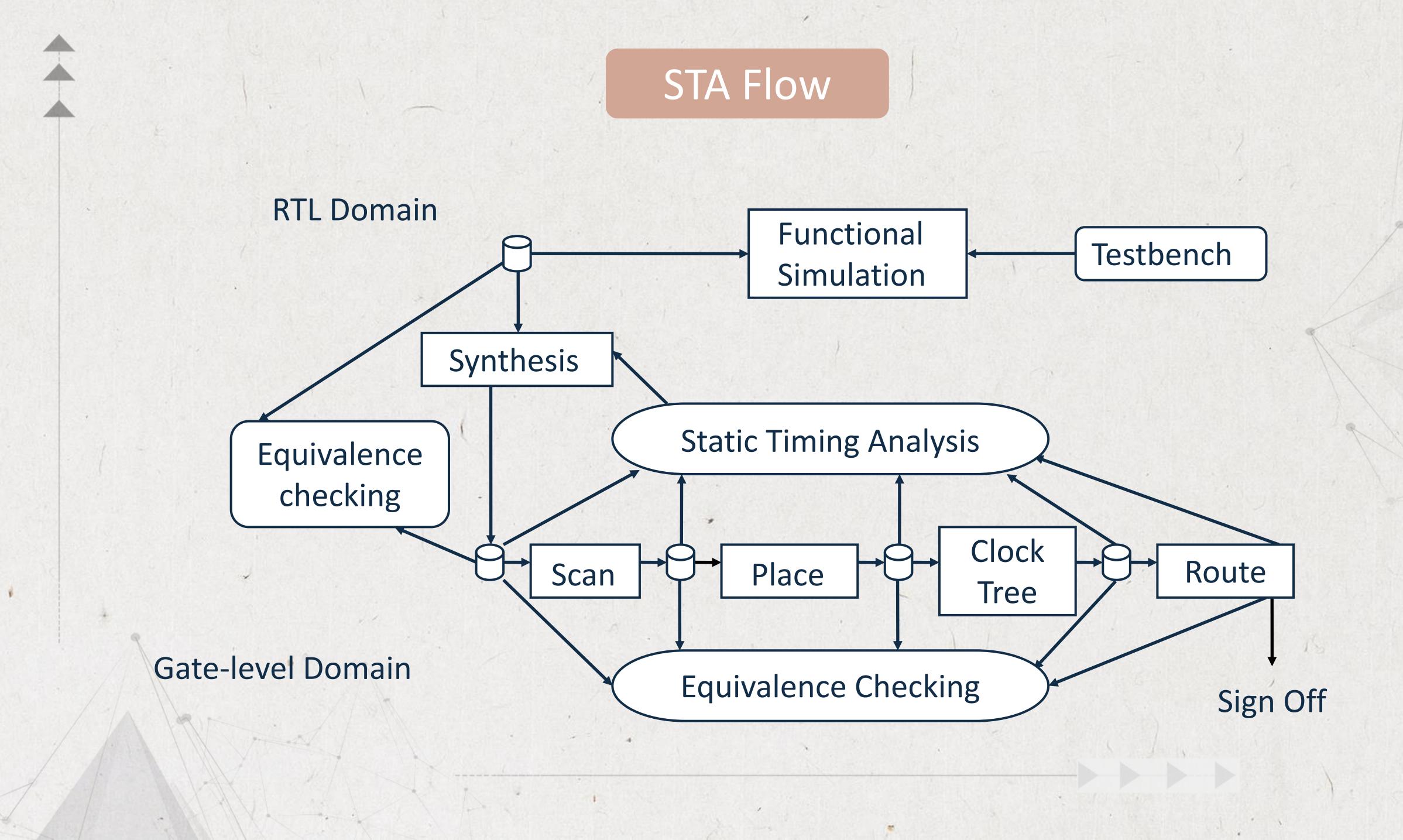

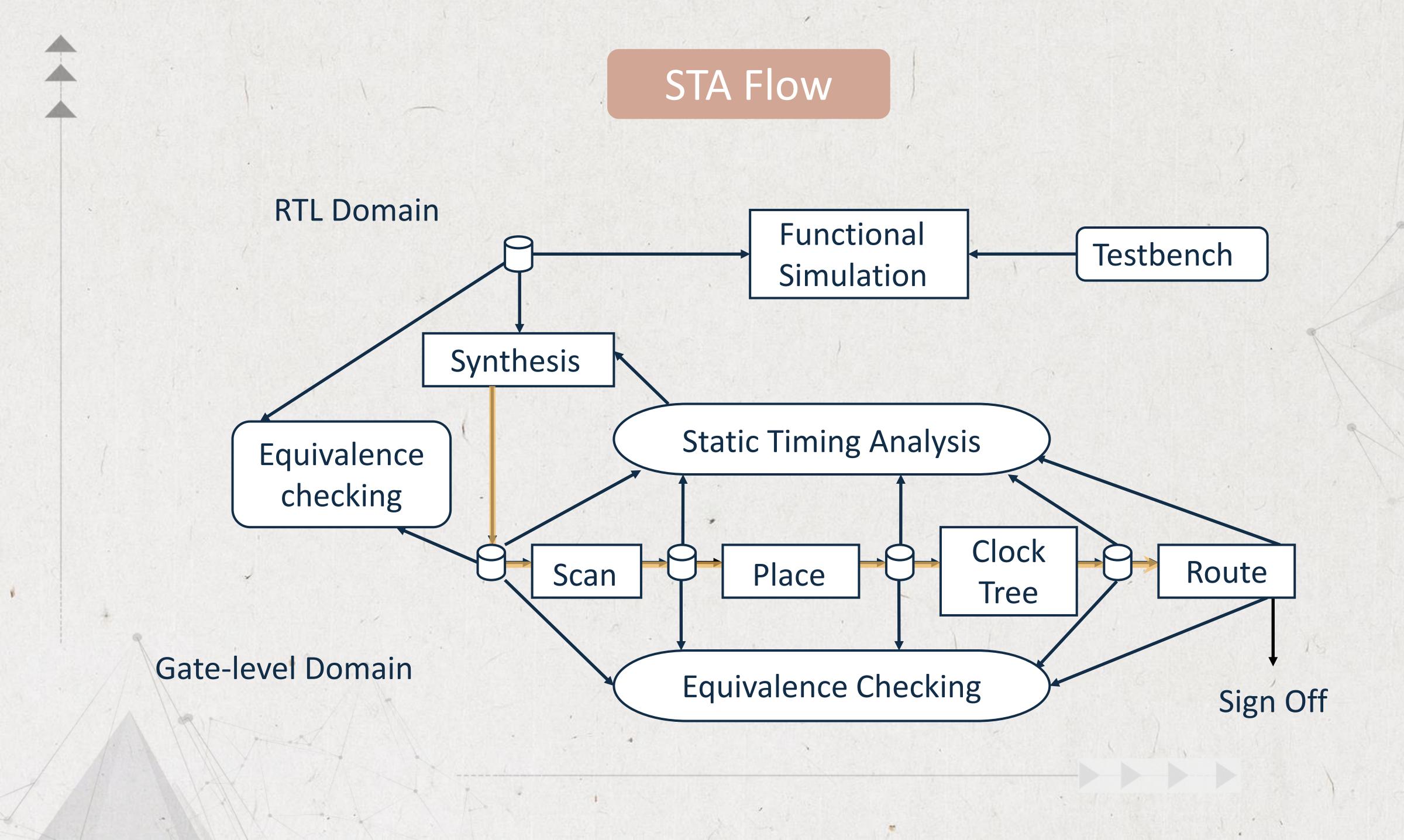

# 回顾:芯片设计流程

# 回顾:芯片设计流程

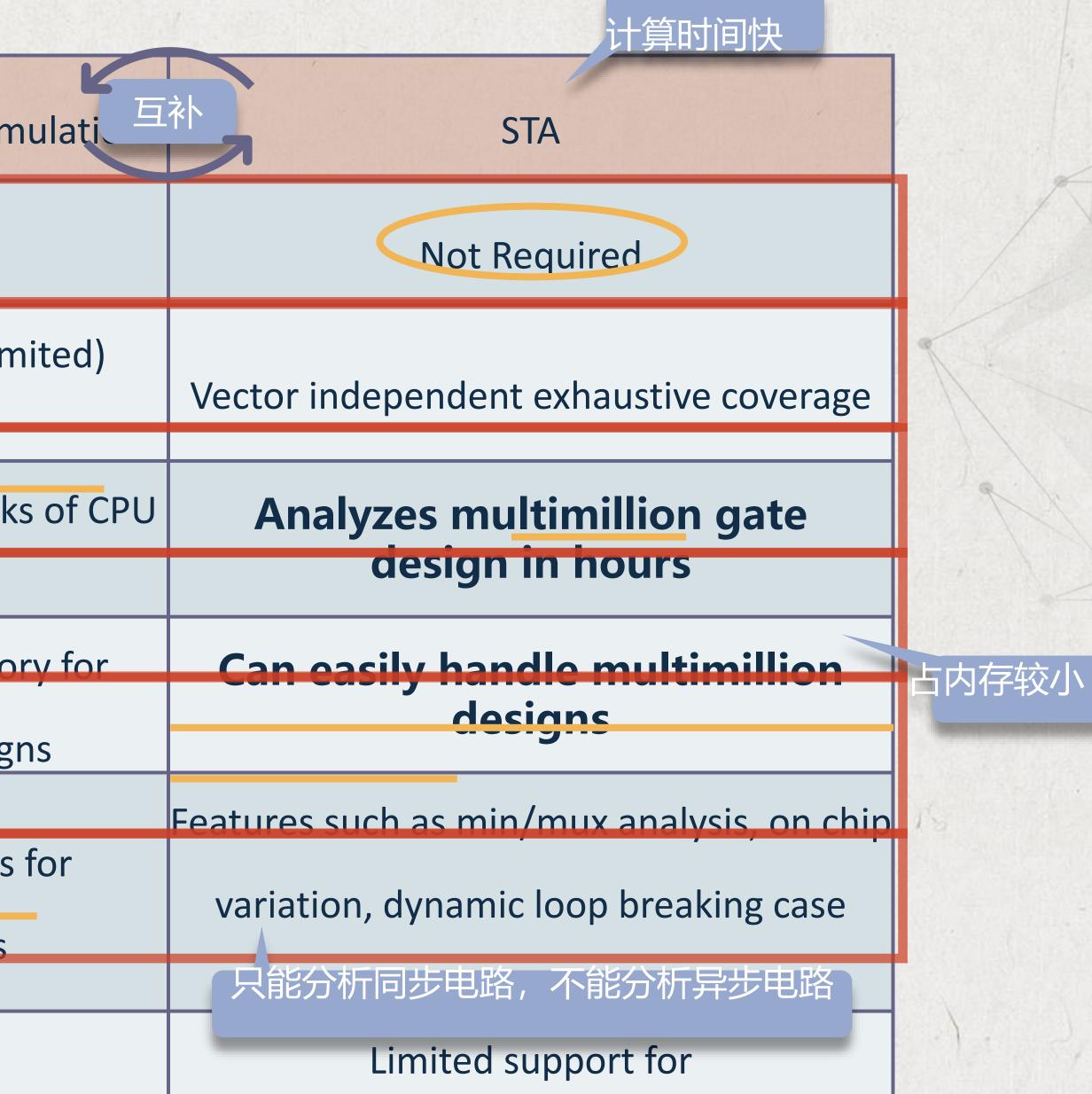

# STA Vs Event Simulation

|                      | Event Driven Timing sin |

|----------------------|-------------------------|

| Vector Generation    | Required                |

| Design Coverage      | Vector dependent(lin    |

|                      | coverage                |

| Dunting              | Takes several days/week |

|                      | time                    |

|                      | Can run out of memo     |

| Capacity             | multimillion desig      |

| Analysis/Debug       | No special features     |

| features             | timing analysis         |

|                      |                         |

| Design style support | No Restrictions         |

· ·

## Prime Time

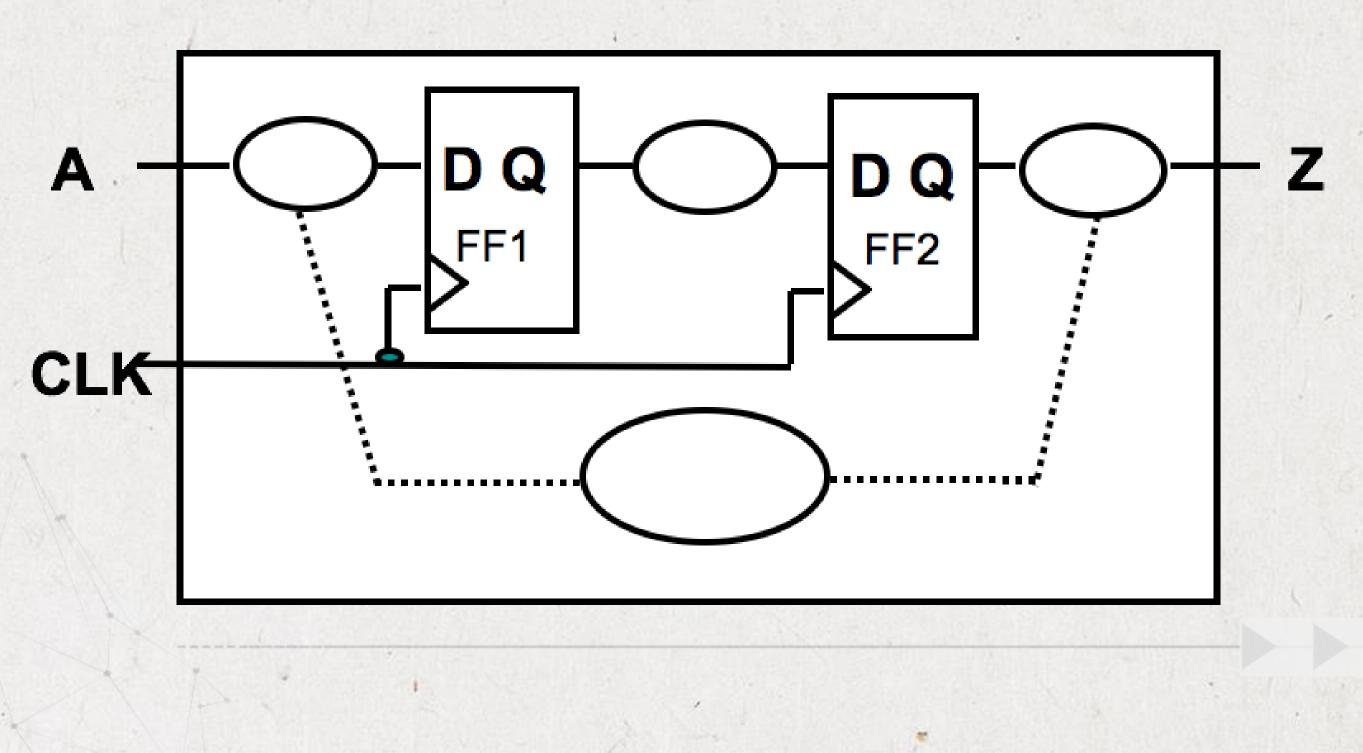

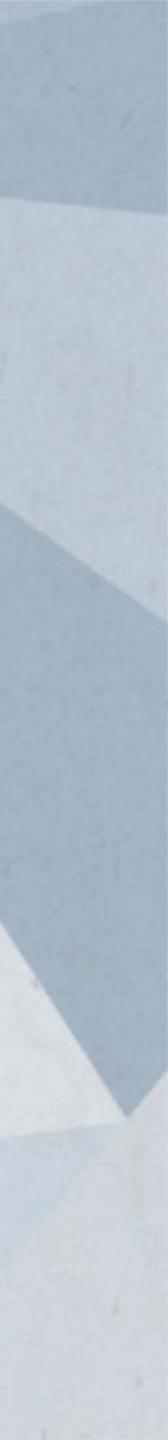

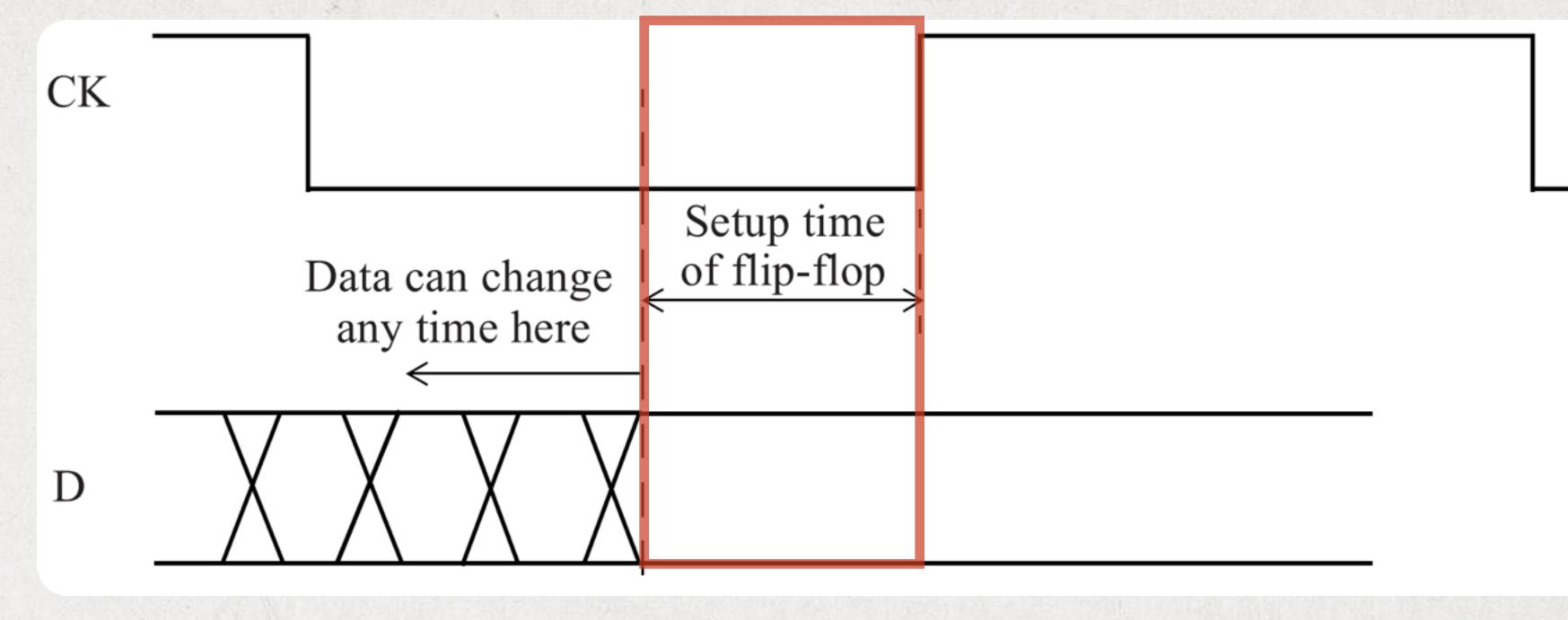

### Setup Time - The length of time that data must stabilize before the clock transition.

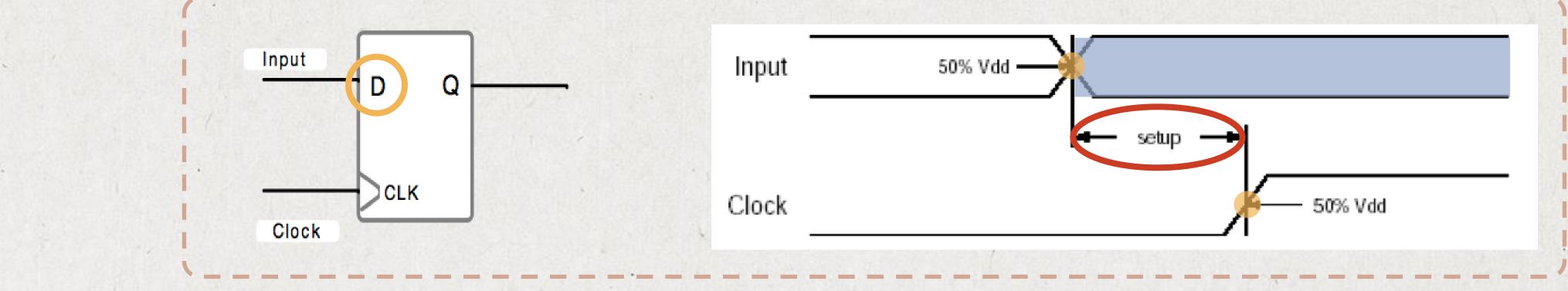

# Hold Time - The length of time that dat active clock transition.

- The length of time that data must remain stable at the input pin after the

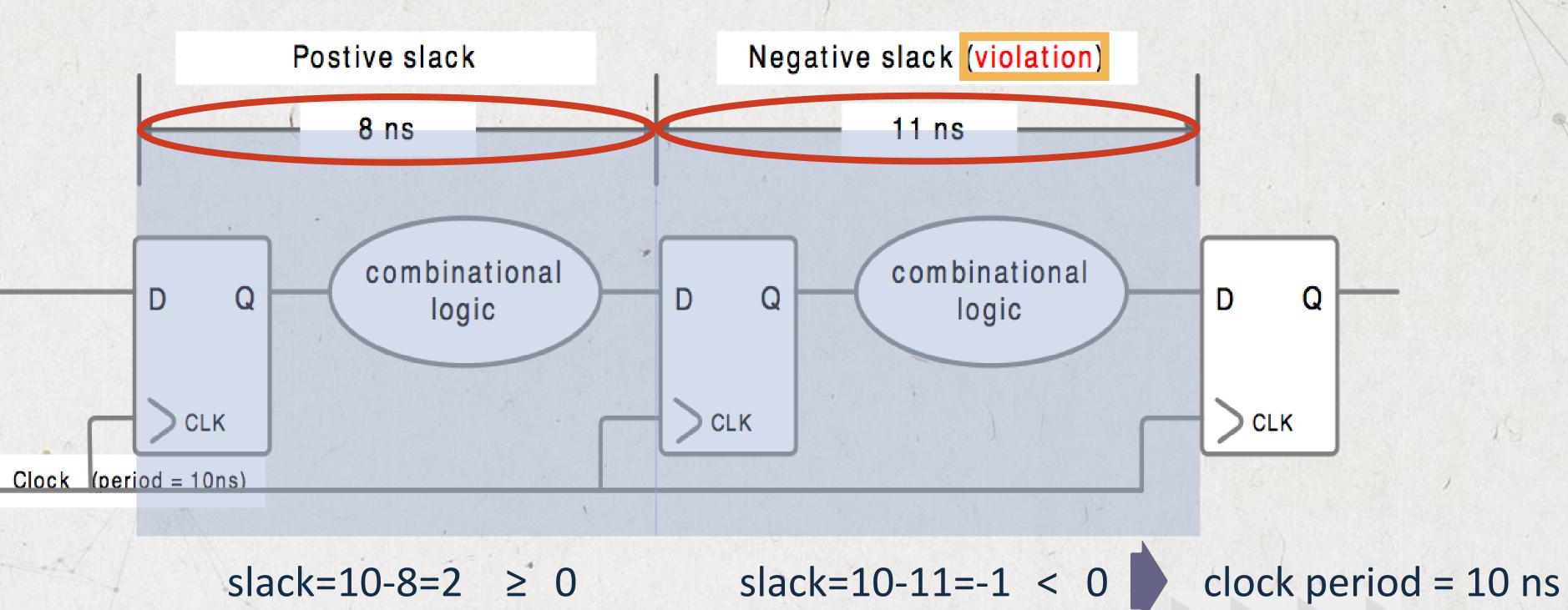

# Time Slack

- Slacks is used to describe how much of the budget did the logic used up.

- Slack the resulting margin between required & actual time of signal traveling in the path.

- Positive slack or zero means meet constraints

- Negative slack means violate constraint

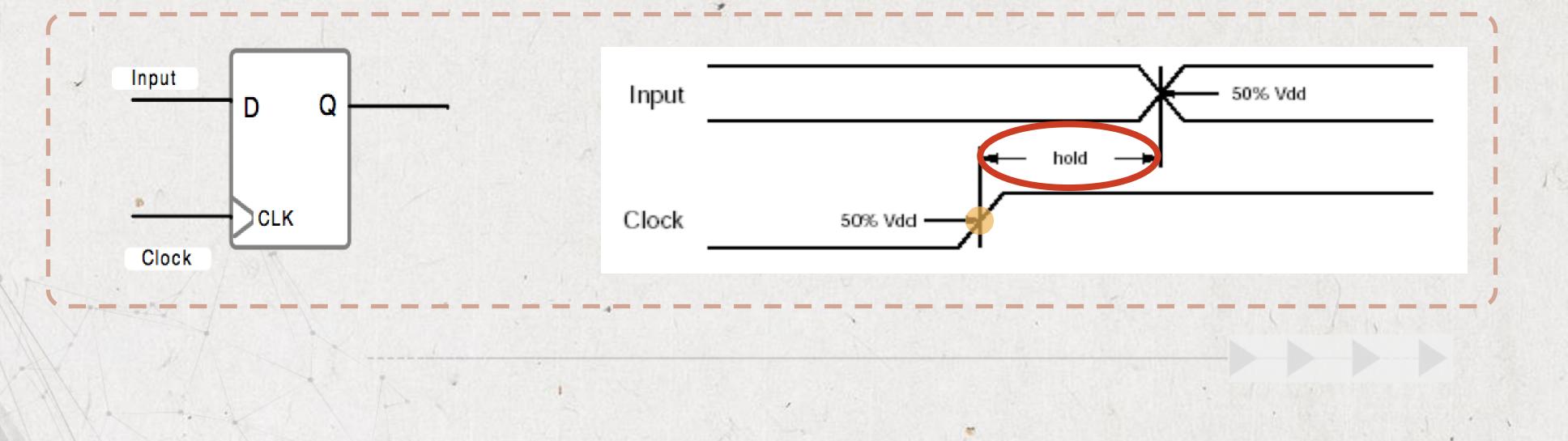

|                | Input | 50% Vdd |  |

|----------------|-------|---------|--|

|                | Clock |         |  |

| and the second |       |         |  |

1 N

• The worst case logic path determine the maximum speed (minimum clock period) for a synchronous system • Example: clock period = 10 ns

#### slack=10-8=2 $\geq 0$

# Speed vs. Slack

# 时钟频率 整个电路的运行速度

### • Large positive slack Large size • Large power •

# Power vs. Slack

### >0 slack

# Three Steps in Static Timing Analysis

#### STA involves three main steps:

Design is broken down into sets of timing paths

Delay of each path is calculated

Path delays are checked to see if timing constraints have been met

工艺库

静态数据分析

逻辑综合

时序分析

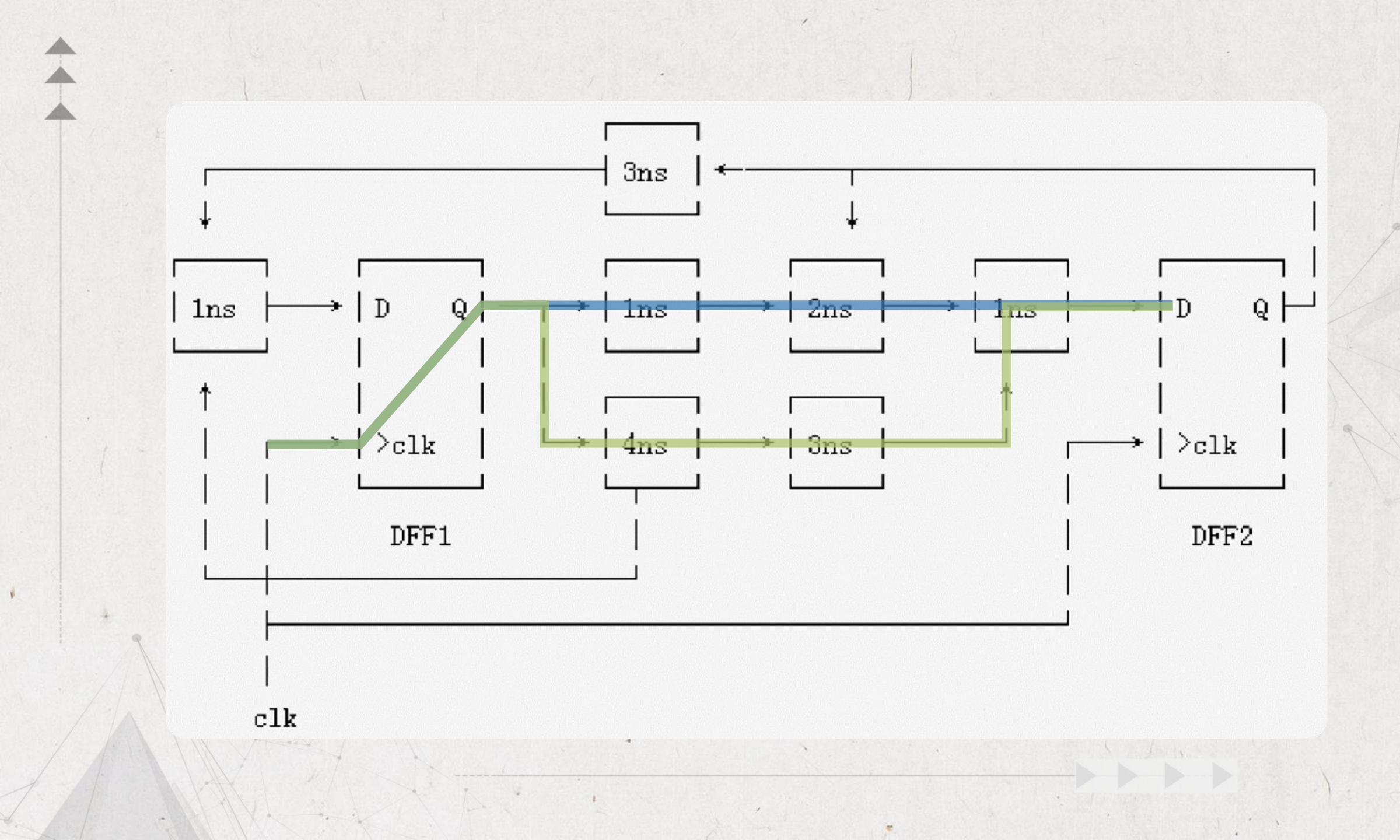

## 时钟网络的延迟=0

## 时钟树的走线延迟、 buffer分布精确

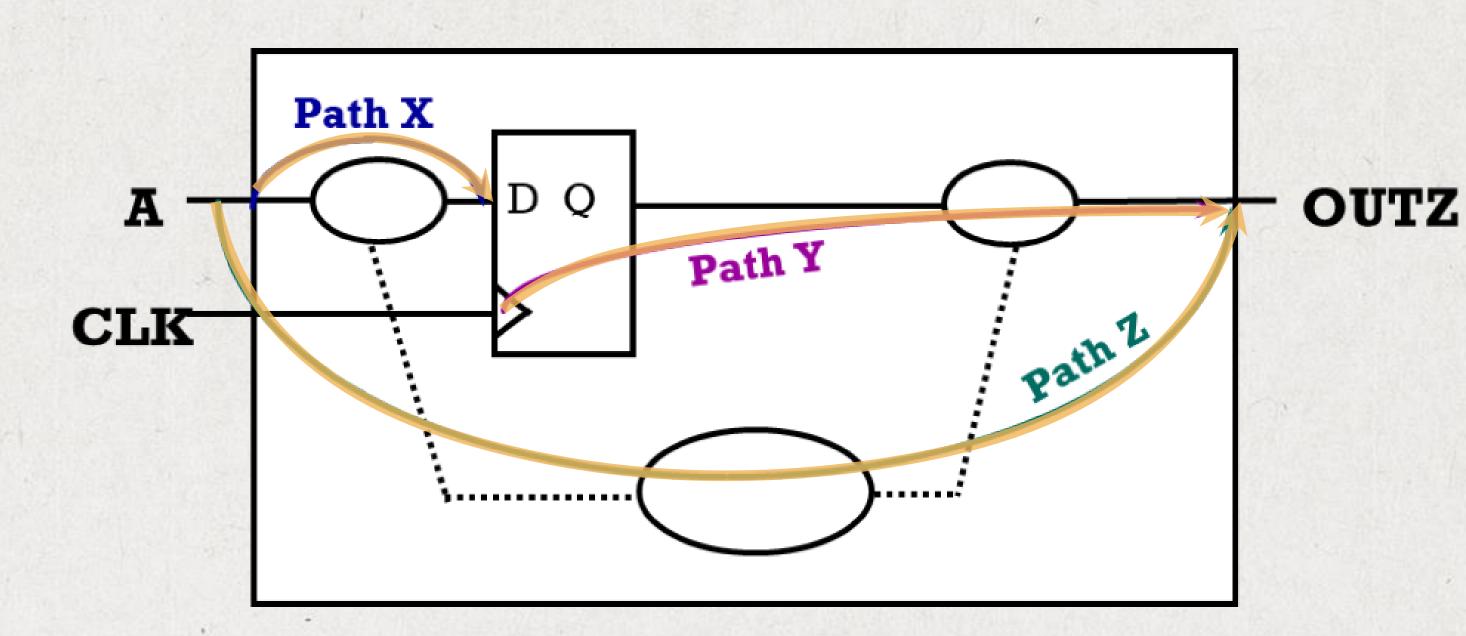

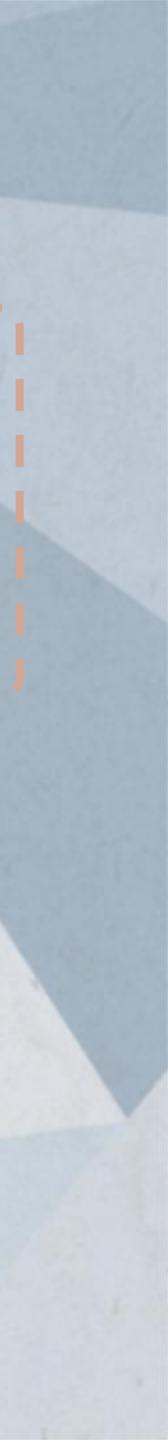

### PrimeTime breaks designs into sets of paths. There are 4 types of PrimeTime paths:

- Input port to data pin of flip-flop (Path 1)

Clock pin of flip-flop to data pin of flip-flop (Path 2)

Clock pin of flip-flop to output port (Path 3)

- Input port to output port (Path 4)

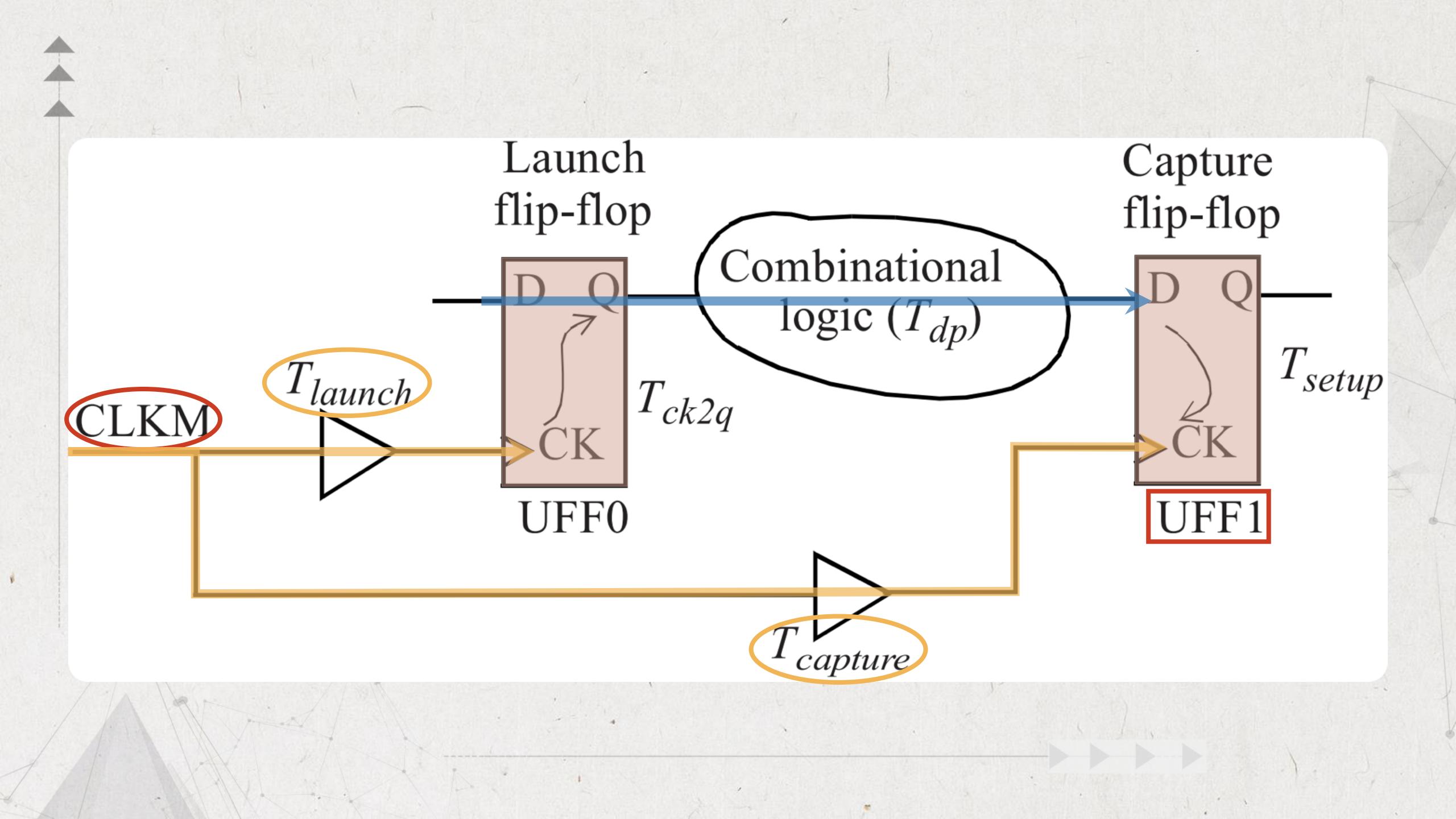

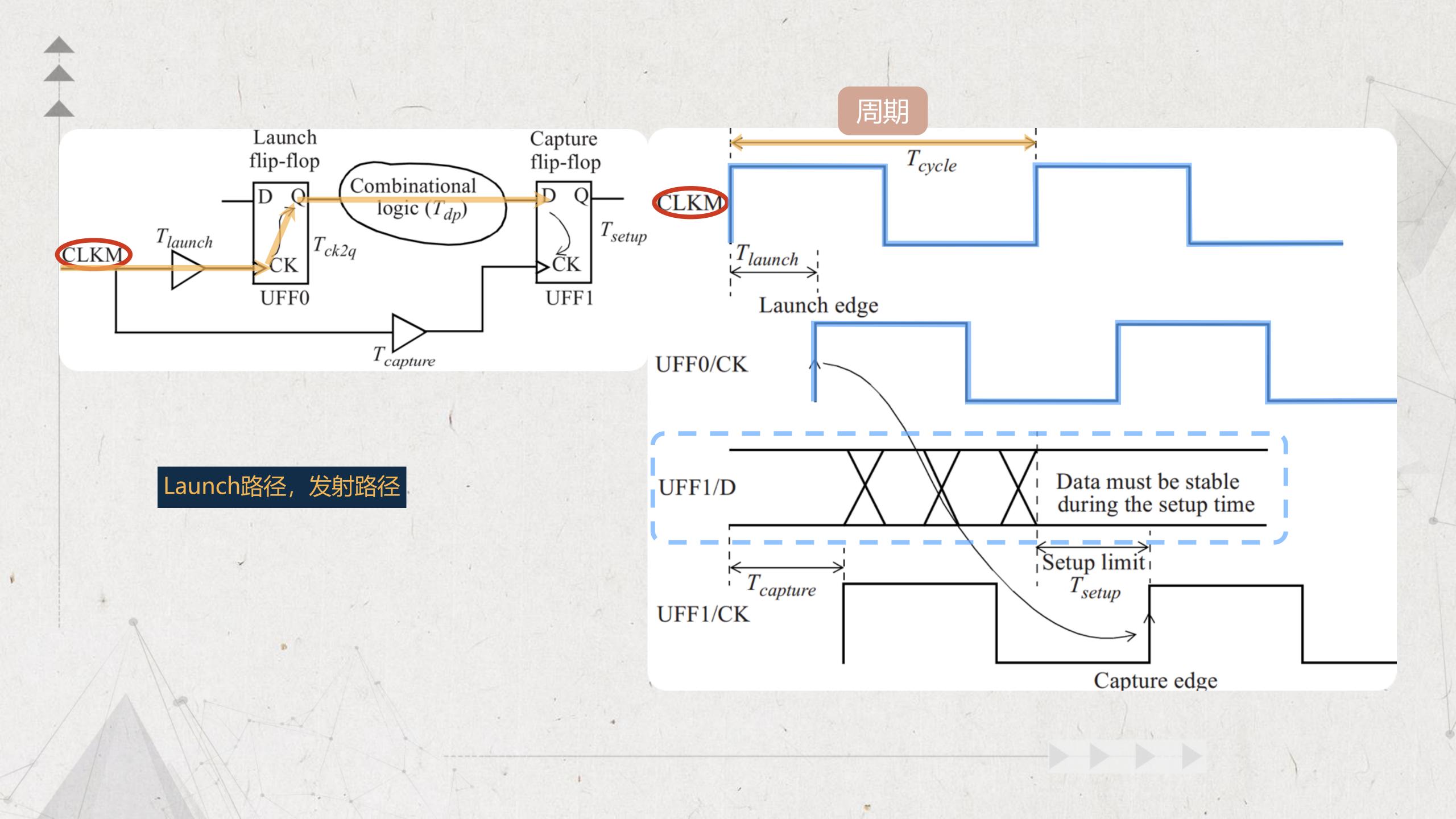

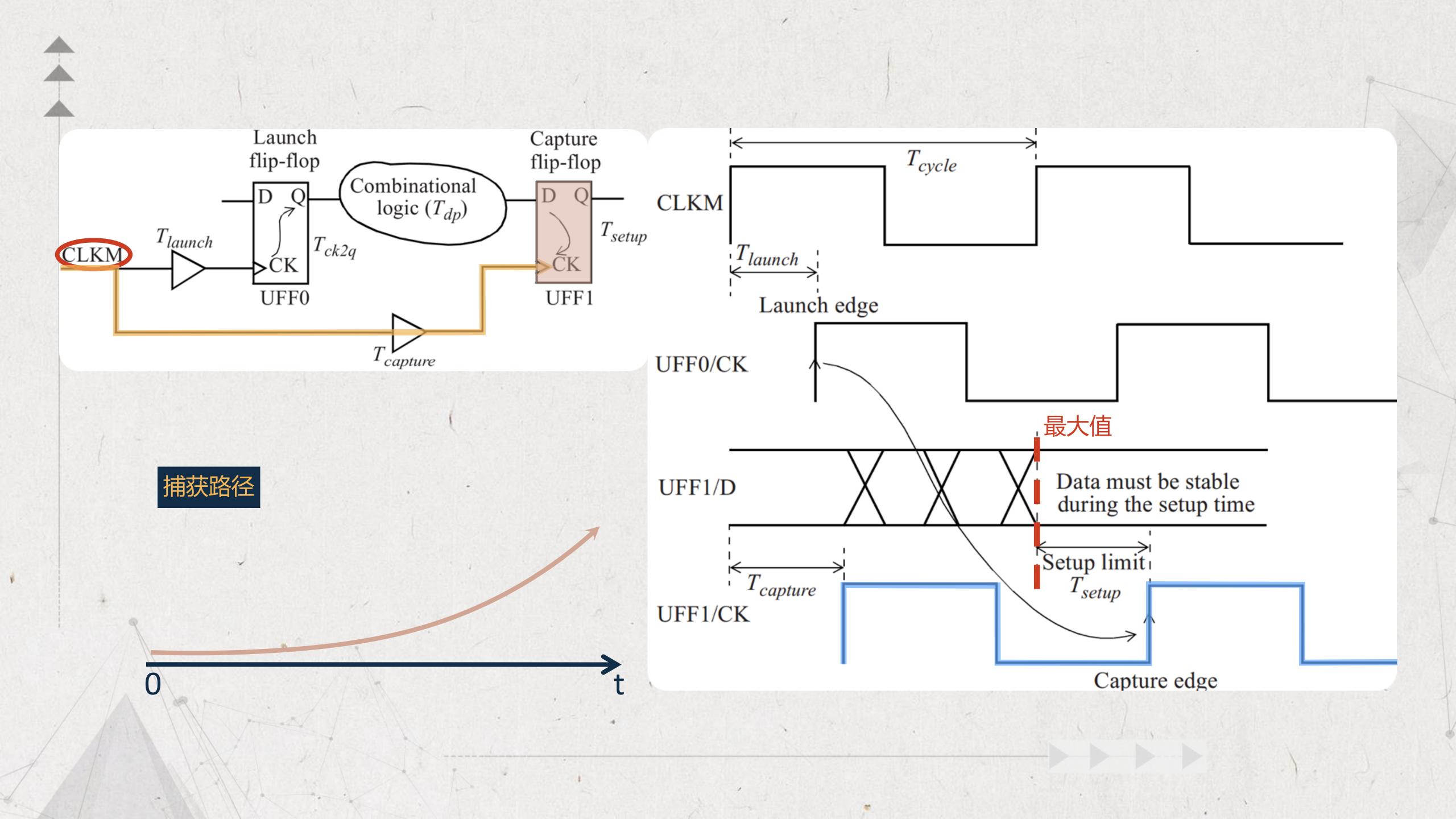

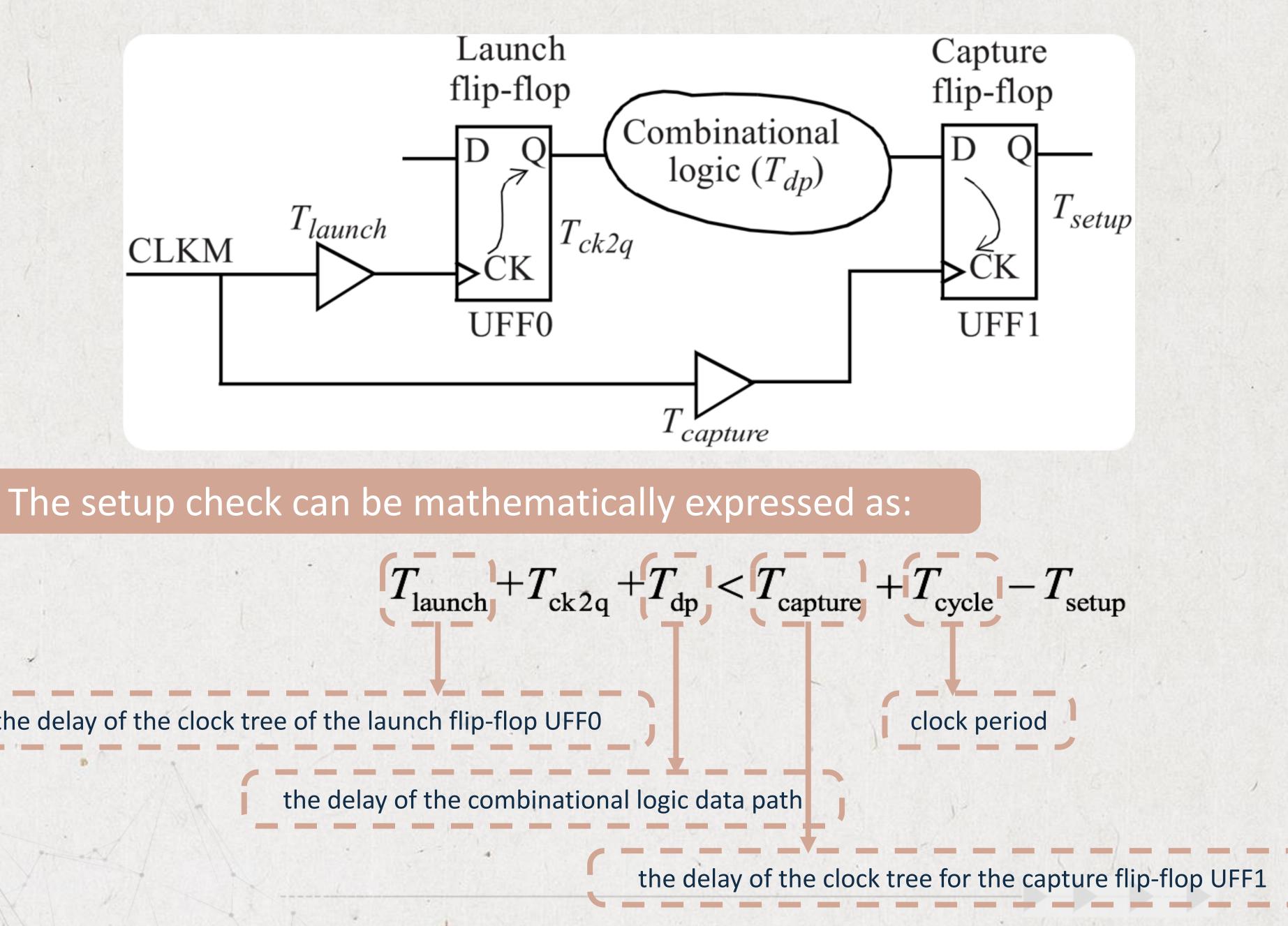

# Setup timing check

### A setup timing check verifies the timing relationship between the clock and the data pin of a flip-flop so that the setup requirement is met.

#### Setup requirement of a flip-flop

the delay of the clock tree of the launch flip-flop UFF0

5 . . .

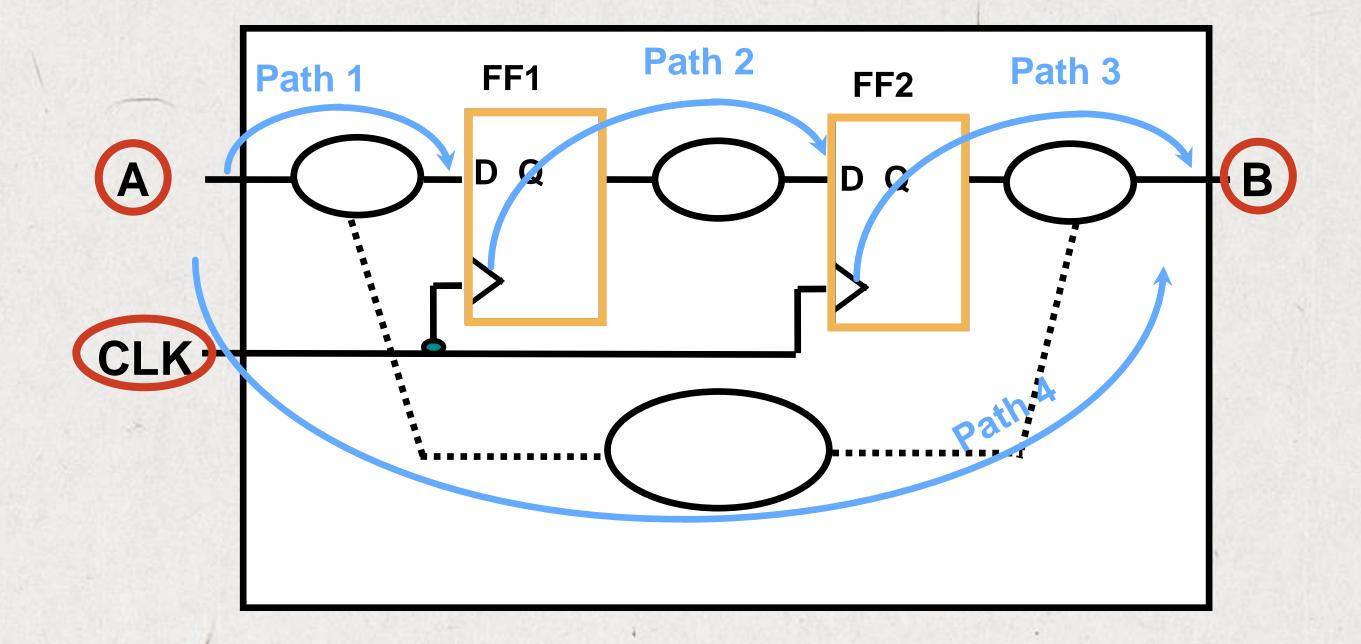

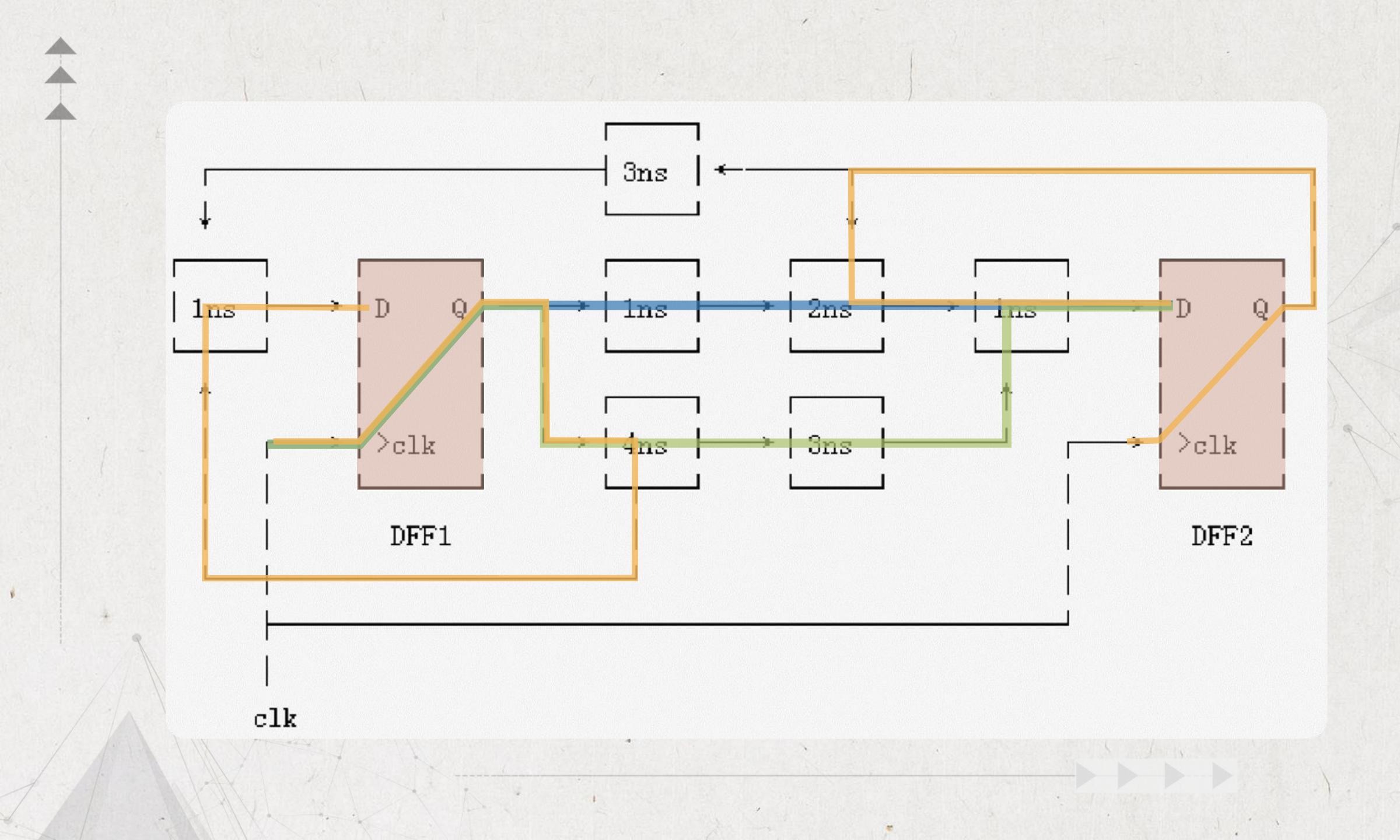

### Flip-flop to Flip-flop Path

Startpoint: UFF0 (rising edge-t Endpoint: UFF1 (rising edge-tri Path Group: CLKM Path Type: max

Point

clock CLKM (rise edge)

clock network delay (ideal)

UFF0/CK (DFF )

UFF0/Q (DFF ) <UNOR0/ZN (NR2 )

UBUF4/Z (BUFF )

UFF1/D (DFF )

data arrival time</pre>

触发器到触发器路径

### Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

| Incr                                 | Path                                       |

|--------------------------------------|--------------------------------------------|

| 0.00<br>0.00<br>0.00<br>0.16<br>0.04 | 0.00<br>0.00<br>0.00 r<br>0.16 f<br>0.20 r |

| 0.05<br>0.00                         | 0.26 r<br>0.26 r<br>0.26                   |

### Flip-flop to Flip-flop Path

clock CLKM (rise edge)

clock network delay (ideal)

clock uncertainty

UFF1/CK (DFF )

library setup time

data required time

data required time data arrival time

slack (MET)

10.00 10.00 9.70 9.70 r

- 9.66

- 9.66

- -0.26

9.41

**10.00** 0.00

- -0.30

- -0.04

# Question

What are the start point and the end point of this path?

② Which Path Group is this path belong to?

③ Path Type?

④ Constrain?