# 芯动力——硬件加速设计方法

第五章 静态时序分析(2)

邸志雄@西南交通大学zxdi@home.swjtu.edu.cn

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

|   | Point                       | Incr | Path   |  |

|---|-----------------------------|------|--------|--|

|   |                             |      |        |  |

| * | clock CLKM (rise edge)      | 0.00 | 0.00   |  |

|   | clock network delay (ideal) | 0.00 | 0.00   |  |

|   | UFF0/CK (DFF )              | 0.00 | 0.00 r |  |

|   | UFF0/Q (DFF ) <-            | 0.16 | 0.16 f |  |

|   | UNOR0/ZN (NR2 )             | 0.04 | 0.20 r |  |

|   | UBUF4/Z (BUFF )             | 0.05 | 0.26 r |  |

|   | UFF1/D (DFF )               | 0.00 | 0.26 r |  |

|   | data arrival time           |      | 0.26   |  |

|   |                             |      |        |  |

| clock CLKM (rise edge)   | 10.00     | 10.00  |

|--------------------------|-----------|--------|

| clock network delay (ide | eal) 0.00 | 10.00  |

| clock uncertainty        | -0.30     | 9.70   |

| UFF1/CK (DFF )           |           | 9.70 r |

| library setup time       | -0.04     | 9.66   |

| data required time       |           | 9.66   |

|                          |           |        |

| data required time       |           | 9.66   |

| data arrival time        |           | -0.26  |

|                          |           |        |

| slack (MET)              |           | 9.41   |

# Question

- 1 What are the start point and the end point of this path?

- 2 Which Path Group is this path belong to?

- 3 Path Type?

- 4 Constrain?

2 which Path Group is this path belong to?

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

Path Type: max

| Point                                    | Incr                   | Path   |

|------------------------------------------|------------------------|--------|

| The Path Group line indicates that it be | longs to the path grou | o CLKM |

| clock CLKM (rise edge)                   | 0.00                   | 0.00   |

| clock network delay (ideal)              | 0.00                   | 0.00   |

| UFF0/CK (DFF )                           | 0.00                   | 0.00 r |

| UFF0/Q (DFF ) <-                         | 0.16                   | 0.16 f |

| UNORO/ZN (NR2 )                          | 0.04                   | 0.20 r |

| UBUF4/Z (BUFF )                          | 0.05                   | 0.26 r |

| UFF1/D (DFF )                            | 0.00                   | 0.26 r |

| data arrival time                        |                        | 0.26   |

1 what are the start point and the end point of this path?

### 3 Path Type?

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

|   | Point                       | Incr | Path   |

|---|-----------------------------|------|--------|

|   |                             |      |        |

| * | clock CLKM (rise edge)      | 0.00 | 0.00   |

|   | clock network delay (ideal) | 0.00 | 0.00   |

|   | UFF0/CK (DFF )              | 0.00 | 0.00 r |

|   | UFF0/Q (DFF ) <-            | 0.16 | 0.16 f |

|   | UNORO/ZN (NR2 )             | 0.04 | 0.20 r |

|   | UBUF4/Z (BUFF )             | 0.05 | 0.26 r |

|   | UFF1/D (DFF )               | 0.00 | 0.26 r |

|   | data arrival time           |      | 0.26   |

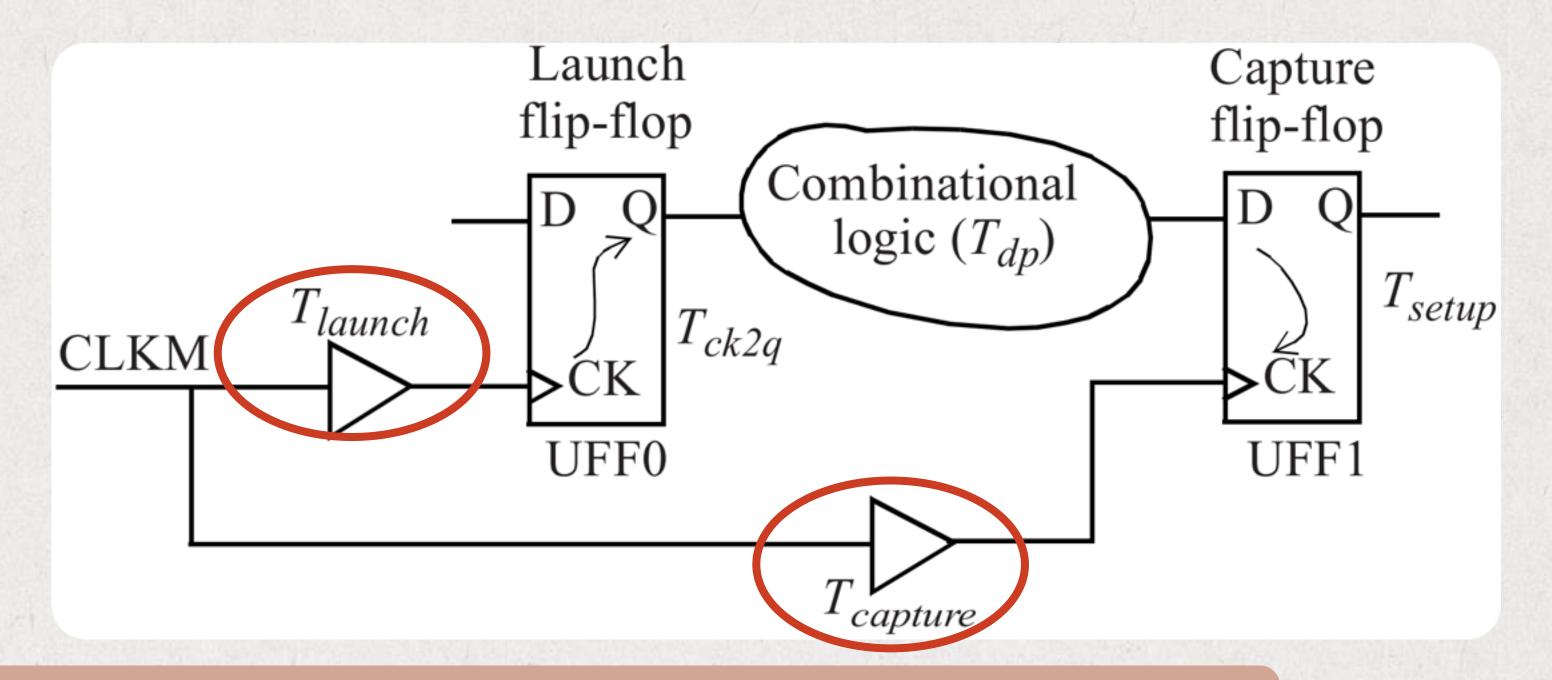

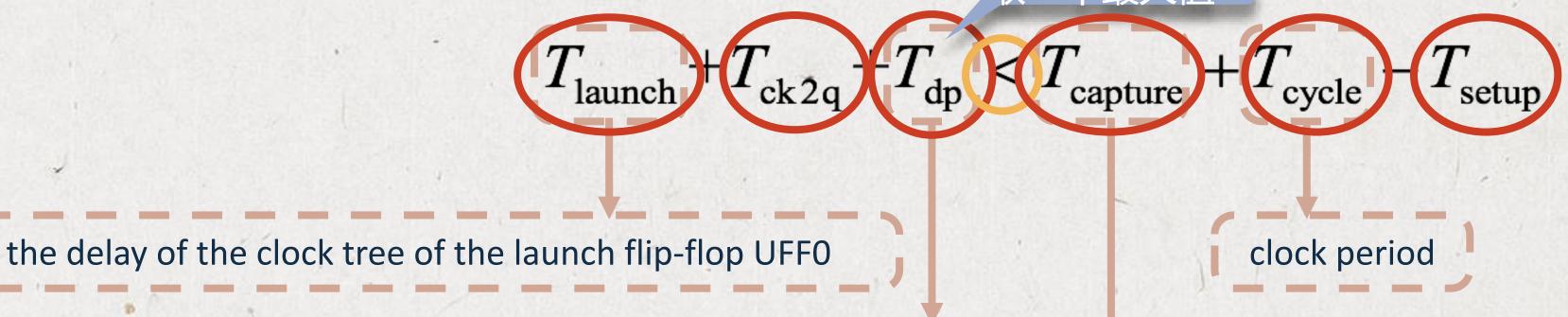

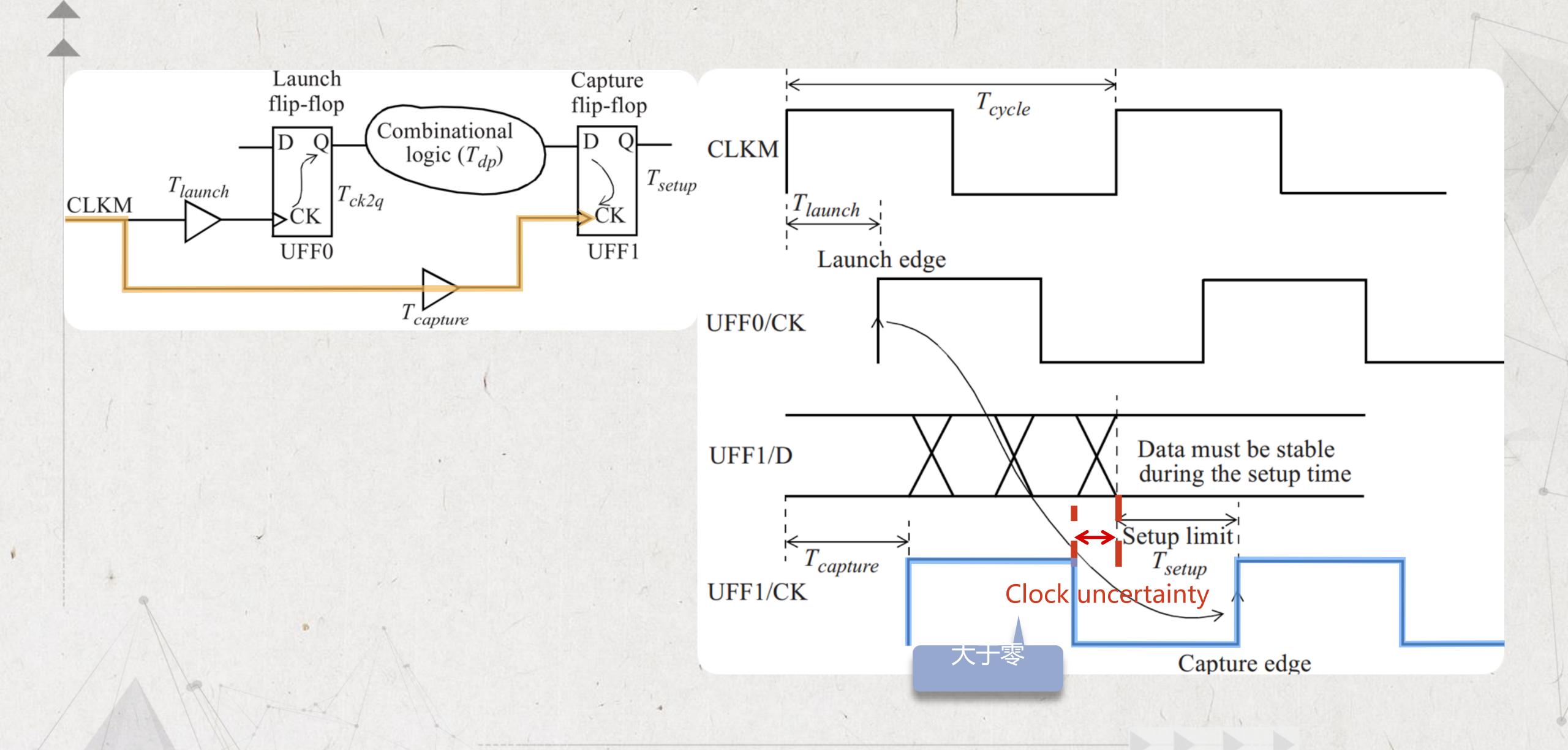

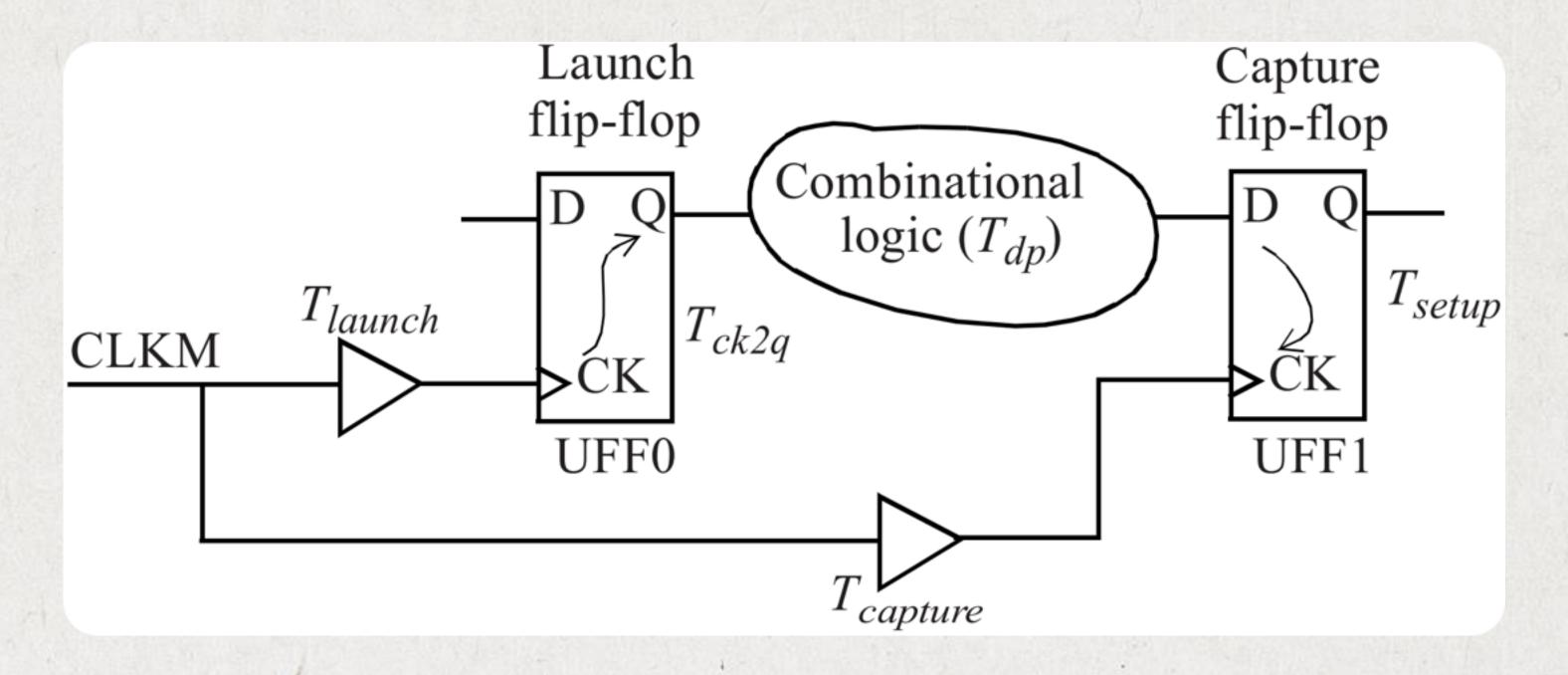

# The setup check can be mathematically ex<sub>取一个最大值</sub>

the delay of the combinational logic data path

the delay of the clock tree for the capture flip-flop UFF1

### 3 Path Type?

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

Path Type: max

min

| Point                       | Incr | Path   |

|-----------------------------|------|--------|

| clock CLKM (rise edge)      | 0.00 | 0.00   |

| clock network delay (ideal) | 0.00 | 0.00   |

| UFF0/CK (DFF )              | 0.00 | 0.00 r |

The Path Type line indicates that the delays shown in this report are all max path delays indicating that this is a setup check.

This is because setup checks correspond to the max (or longest path) delays through the logic.

Note that the hold checks correspond to the min (or shortest path) delays through the logic.

| clock CLKM (rise edge)      | 10.00 | 10.00  |

|-----------------------------|-------|--------|

| clock network delay (ideal) | 0.00  | 10.00  |

| clock uncertainty           | -0.30 | 9.70   |

| UFF1/CK (DFF )              |       | 9.70 r |

| library setup time          | -0.04 | 9.66   |

| data required time          |       | 9.66   |

|                             |       |        |

| data required time          |       | 9.66   |

| data arrival time           |       | -0.26  |

|                             |       |        |

| slack (MET)                 |       | 9.41   |

# 4 Constrain?

| create_clock -name C                 | LKM -period 10 -waveform {0 5} [g | et_ports CLKM] |

|--------------------------------------|-----------------------------------|----------------|

| clock CLKM (rise edge)               | 10.00                             | 10.00          |

| clock network delay (ideal)          | 0.00                              | 10.00          |

| clock uncertainty                    | -0.30                             | 9.70           |

| UFF1/CK (DFF )                       |                                   | 9.70 r         |

| library setup time                   | -0.04                             | 9.66           |

| data required time                   |                                   | 9.66           |

| data required time data arrival time |                                   | 9.66           |

|                                      |                                   |                |

| slack (MET)                          |                                   | 9.41           |

set\_ideal\_network

dont\_touch

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

|   | Point                       | Incr | Path   |   |

|---|-----------------------------|------|--------|---|

| , | clock CLKM (rise edge)      | 0.00 | 0.00   | _ |

|   | clock network delay (ideal) | 0.00 | 0.00   |   |

|   | UFF0/CK (DFF )              | 0.00 | 0.00 r |   |

|   | UFF0/Q (DFF ) <-            | 0.16 | 0.16 f |   |

|   | UNOR0/ZN (NR2 )             | 0.04 | 0.20 r |   |

|   | UBUF4/Z (BUFF )             | 0.05 | 0.26 r |   |

|   | UFF1/D (DFF )               | 0.00 | 0.26 r |   |

|   | data arrival time           |      | 0.26   |   |

|   |                             |      |        |   |

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

|   | Point                       | Incr                         | Path   |

|---|-----------------------------|------------------------------|--------|

|   |                             |                              |        |

| * | clock CLKM (rise edge)      | 0.00                         | 0.00   |

|   | clock network delay (ideal) | 0.00                         | 0.00   |

|   | UFF0/CK (DFF )              | 0.00                         | 0.00 r |

|   | UFF0/Q (DFF ) <-            | $T_{\text{launch}} = 0$ 0.16 | 0.16 f |

|   | UNORO/ZN (NR2 )             | 0.04                         | 0.20 r |

|   | UBUF4/Z (BUFF )             | 0.05                         | 0.26 r |

|   | UFF1/D (DFF )               | 0.00                         | 0.26 r |

|   | data arrival time           |                              | 0.26   |

|   |                             |                              |        |

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

| clock CLKM (rise edge) 0.00 0.00            |  |

|---------------------------------------------|--|

| clock network delay (ideal) 0.00 0.00       |  |

| UFF0/CK (DFF ) $T = 0.00$ 0.00 r            |  |

| $T_{\rm ck2q} = 0.16 \qquad 0.00  {\rm fm}$ |  |

| UNOR0/ZN (NR2 ) 0.20 r                      |  |

| UBUF4/Z (BUFF ) 0.26 r                      |  |

| UFF1/D (DFF ) 0.00 0.26 r                   |  |

| data arrival time 0.26                      |  |

| clock CLKM (rise edge)      | 10.00 | 10.00  |

|-----------------------------|-------|--------|

| clock network delay (ideal) | 0.00  | 10.00  |

| clock uncertainty           | -0.30 | 9.70   |

| UFF1/CK (DFF )              |       | 9.70 r |

| library setup time          | -0.04 | 9.66   |

| data required time          |       | 9.66   |

|                             |       |        |

| data required time          |       | 9.66   |

| data arrival time           |       | -0.26  |

|                             |       |        |

| slack (MET)                 |       | 9.41   |

| clock CLKM (rise edge)                    | 10.00 | 10.00  |

|-------------------------------------------|-------|--------|

| clock network delay (ideal)               | 0.00  | 10.00  |

| clock uncertainty                         | -0.30 | 9.70   |

| UFF1/CK (DFF )                            |       | 9.70 r |

| library setup time $T_{\rm setup} = 0.04$ | -0.04 | 9.66   |

| data required time                        |       | 9.66   |

|                                           |       |        |

| data required time                        |       | 9.66   |

| data arrival time                         |       | -0.26  |

|                                           |       |        |

| slack (MET)                               |       | 9.41   |

|     | clock CLKM (rise edge)      | 10.00 | 10.00  |

|-----|-----------------------------|-------|--------|

|     | clock network delay (ideal) | 0.00  | 10.00  |

| 100 | clock uncertainty           | -0.30 | 9.70   |

|     | UFF1/CK (DFF )              |       | 9.70 r |

|     | library setup time          | -0.04 | 9.66   |

| *   | data required time          |       | 9.66   |

|     |                             |       |        |

|     | data required time          |       | 9.66   |

|     | data arrival time           |       | -0.26  |

|     |                             |       |        |

|     | slack (MET)                 |       | 9.41   |

| clock CLKM (rise edge)      | 10.00 | 10.00  |

|-----------------------------|-------|--------|

| clock network delay (ideal) | 0.00  | 10.00  |

| clock uncertainty           | -0.30 | 9.70   |

| UFF1/CK (DFF )              |       | 9.70 r |

| library setup time          | -0.04 | 9.66   |

| data required time          |       | 9.66   |

|                             |       |        |

| data required time          |       | 9.66   |

| data arrival time           |       | -0.26  |

|                             |       |        |

| slack (MET)                 |       | 9.41   |

$$T_{\rm launch} + T_{\rm ck\,2q} + T_{\rm dp} < T_{\rm capture} + T_{\rm cycle} - T_{\rm setup}$$

$$slack = (T_{capture} + T_{cycle} - T_{setup} - T_{uncertainty}) - (T_{launch} + T_{ck2q} + T_{dp})$$

$$0 + 10 - {0.0 \choose 4} - {0.3 \choose 0}$$

$$0 + {0.1 \choose 6} + {0.0 \choose 9}$$

Data required time

Data arrival time

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

| Point                       | Incr | Path   |

|-----------------------------|------|--------|

| clock CLKM (rise edge)      | 0.00 | 0.00   |

| clock network delay (ideal) | 0.00 | 0.00   |

| UFF0/CK (DFF )              | 0.00 | 0.00 r |

| UFF0/Q (DFF ) <-            | 0.16 | 0.16 f |

| UNORO/ZN (NR2 )             | 0.04 | 0.20 r |

| UBUF4/Z (BUFF )             | 0.05 | 0.26 r |

| UFF1/D (DFF )               | 0.00 | 0.26 r |

| data arrival time           |      | 0.26   |

| clock CLKM (rise edge)      | 10.00 | 10.00  |

|-----------------------------|-------|--------|

| clock network delay (ideal) | 0.00  | 10.00  |

| clock uncertainty           | -0.30 | 9.70   |

| UFF1/CK (DFF )              |       | 9.70 r |

| library setup time          | -0.04 | 9.66   |

| data required time          |       | 9.66   |

|                             |       |        |

| data required time          |       | 9.66   |

| data arrival time           |       | -0.26  |

|                             |       |        |

| slack (MET)                 |       | 9.41   |

### 时钟网络有一个确定值的延迟值

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKM

| Point                            | Incr | Path   |

|----------------------------------|------|--------|

|                                  |      |        |

| clock CLKM (rise edge)           | 0.00 | 0.00   |

| clock network delay (propagated) | 0.11 | 0.11   |

| UFF0/CK (DFF )                   | 0.00 | 0.11 r |

| UFF0/Q (DFF ) <-                 | 0.14 | 0.26 f |

| UNOR0/ZN (NR2 )                  | 0.04 | 0.30 r |

| UBUF4/Z (BUFF )                  | 0.05 | 0.35 r |

| UFF1/D (DFF )                    | 0.00 | 0.35 r |

| data arrival time                |      | 0.35   |

| clock CLKM (rise ed | ge)          | 10.00 | 10.00  |

|---------------------|--------------|-------|--------|

| clock network delay | (propagated) | 0.12  | 10.12  |

| clock uncertainty   |              | -0.30 | 9.82   |

| UFF1/CK (DFF )      |              |       | 9.82 r |

| library setup time  |              | -0.04 | 9.78   |

| data required time  |              |       | 9.78   |

|                     |              |       |        |

| data required time  |              |       | 9.78   |

| data arrival time   |              |       | -0.35  |

|                     |              |       |        |

| slack (MET)         |              |       | 9.43   |

-

- 4

A Department

0.12 - 0.11 = 0.01

时钟的偏斜

• The timing path report can optionally include the expanded clock paths, that is,

with the clock trees explicitly shown. Here is such an example.

| Point                  | Incr | Path          |

|------------------------|------|---------------|

| clock CLKM (rise edge) | 0.00 | 0.00          |

| clock source latency   | 0.00 | 0.00          |

| CLKM (in)              | 0.00 | 0.00 r        |

| UCKBUF0/C (CKB )       | 0.06 | 0.06 r        |

| UCKBUF1/C (CKB )       | 0.06 | 0.11 r        |

| UFF0/CK (DFF )         | 0.00 | 0.11 r        |

| UFF0/Q (DFF ) <-       | 0.14 | 0.26 <b>f</b> |

| UNOR0/ZN (NR2 )        | 0.04 | 0.30 r        |

| UBUF4/Z (BUFF )        | 0.05 | 0.35 r        |

| UFF1/D (DFF )          | 0.00 | 0.35 <b>r</b> |

| data arrival time      |      | 0.35          |

| clock CLKM (rise edge) | 10.00 | 10.00   |

|------------------------|-------|---------|

| clock source latency   | 0.00  | 10.00   |

| CLKM (in)              | 0.00  | 10.00 r |

| UCKBUF0/C (CKB )       | 0.06  | 10.06 r |

| UCKBUF2/C (CKB )       | 0.07  | 10.12 r |

| UFF1/CK (DFF )         | 0.00  | 10.12 r |

| clock uncertainty      | -0.30 | 9.82    |

| library setup time     | -0.04 | 9.78    |

| data required time     |       | 9.78    |

|                        |       |         |

| data required time     |       | 9.78    |

| data arrival time      |       | -0.35   |

|                        |       |         |

| slack (MET)            |       | 9.43    |

\* 10.14

• The "r" and "f" characters in the timing report indicate the rising (and falling) edge of the clock or data signal. The previous path report shows the path starting from the falling edge of UFF0/Q and ending on the rising edge of UFF1/D. Since UFF1/D can be either 0 or 1, there can be

a path ending at the falling edge of UFF1/D as well Here is such a pathed by CLKM)

Path Group: CLKM Path Type: max

| Point                  | Incr Path           |

|------------------------|---------------------|

|                        |                     |

| clock CLKM (rise edge) | 从逻辑零翻转到逻辑1产生的延迟     |

| clock source latency   | 0.00 0.00           |

| CLKM (in)              | 0.00 0.00 <b>r</b>  |

| UCKBUF0/C (CKB )       | 0.06 0.06 <b>r</b>  |

| UCKBUF1/C (CKB )       | 0.06 0.11 <b>r</b>  |

| UFF0/CK (DFF )         | 0.00 0.11 <b>r</b>  |

| UFF0/Q (DFF ) <-       | 0.14 0.26 <b>r</b>  |

| UNORO/ZN (NR2 )        | 0.02 0.28 <b>f</b>  |

| UBUF4/Z (BUFF )        | 0.06 0.33 <b>f</b>  |

| UFF1/D (DFF )          | 0.00 0.33 <b>f</b>  |

| data arrival time      | 从逻辑1翻转到逻辑0产生的延迟0.33 |

Note that the edge at the clock pin of the flip-flop (called the active edge) remains unchanged. It can only be a rising or falling active edge, depending upon whether the flip-flop

|     |                        |       |                | 1    |

|-----|------------------------|-------|----------------|------|

|     | clock CLKM (rise edge) | 10.00 | 10.00          |      |

|     | clock source latency   | 0.00  | 10.00          |      |

|     | CLKM (in)              | 0.00  | 10.00 r        | 8    |

|     | UCKBUF0/C (CKB )       | 0.06  | 10.06 r        | Cont |

|     | UCKBUF2/C (CKB )       | 0.07  | 10.12 <b>r</b> | 8    |

| 375 | UFF1/CK (DFF )         | 0.00  | 10.12 r        |      |

|     | clock uncertainty      | -0.30 | 9.82           | 100  |

|     | library setup time     | -0.03 | 9.79           |      |

|     | data required time     |       | 9.79           |      |

|     |                        |       |                |      |

|     | data required time     |       | 9.79           |      |

|     | data arrival time      |       | -0.33          |      |

|     |                        |       |                |      |

| 1   | slack (MET)            |       | 9.46           |      |

|     |                        |       |                | -    |

### What is clock source latency?

• This is also called insertion delay and is the time it takes for a clock to propagate from its source to the clock definition point of the design under analysis as depicted in Figure. This corresponds to the latency of the clock tree that is outside of the design. For example, if this design were part of a larger block, the clock source latency specifies the delay of the clock tree up to the clock pin of the design under analysis. This latency can be explicitly specified using

the set\_clock\_latency command.

CLKM

MAINCLK

Clock source latency (insertion delay)

Clock network latency

clock\_latency

set\_clock\_latency -source -rise 0.7 [get\_clocks CLKM]

set\_clock\_latency -source -fall 0.65 [get\_clocks CLKM]