# 芯动力——硬件加速设计方法

第五章 静态时序分析(4)

邸志雄@西南交通大学 zxdi@home.swjtu.edu.cn

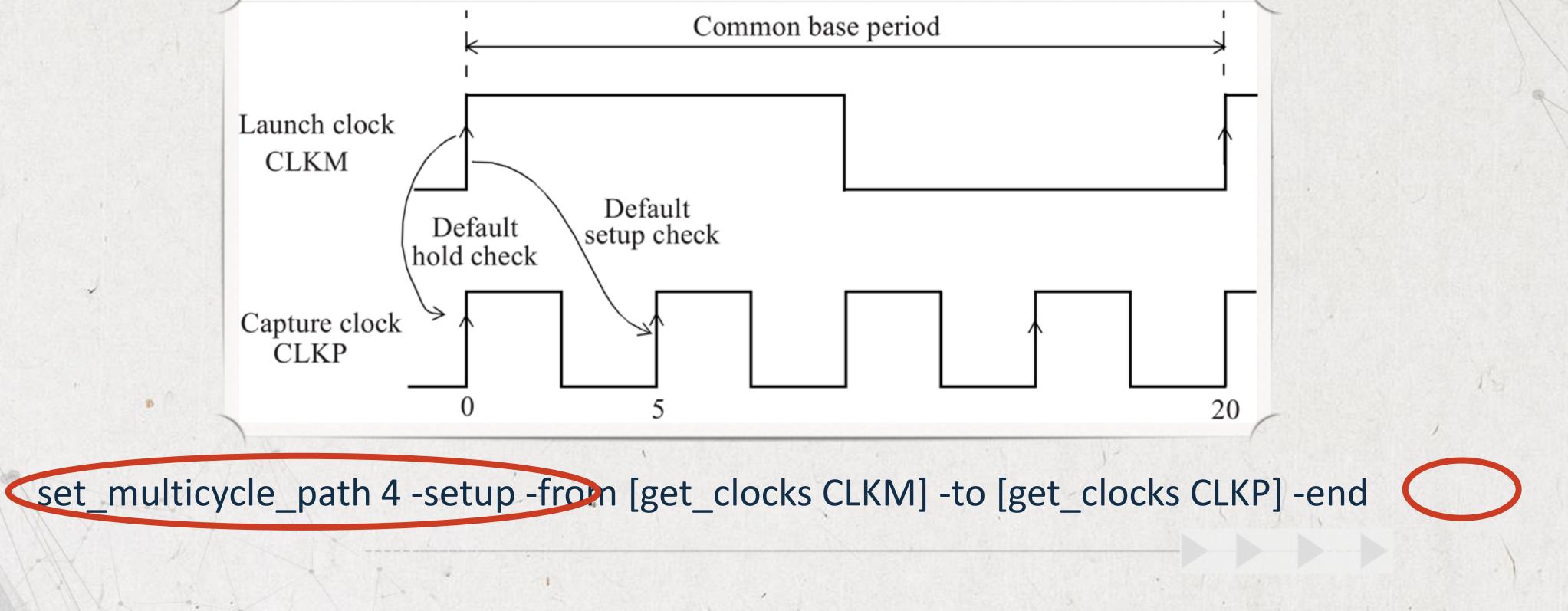

Here are the clock definitions for our example. create\_clock -name CLKM -period 20 -waveform {0 10} [get\_ports CLKM] create\_clock -name CLKP -period 5 -waveform {0 2.5} [get\_ports CLKP]

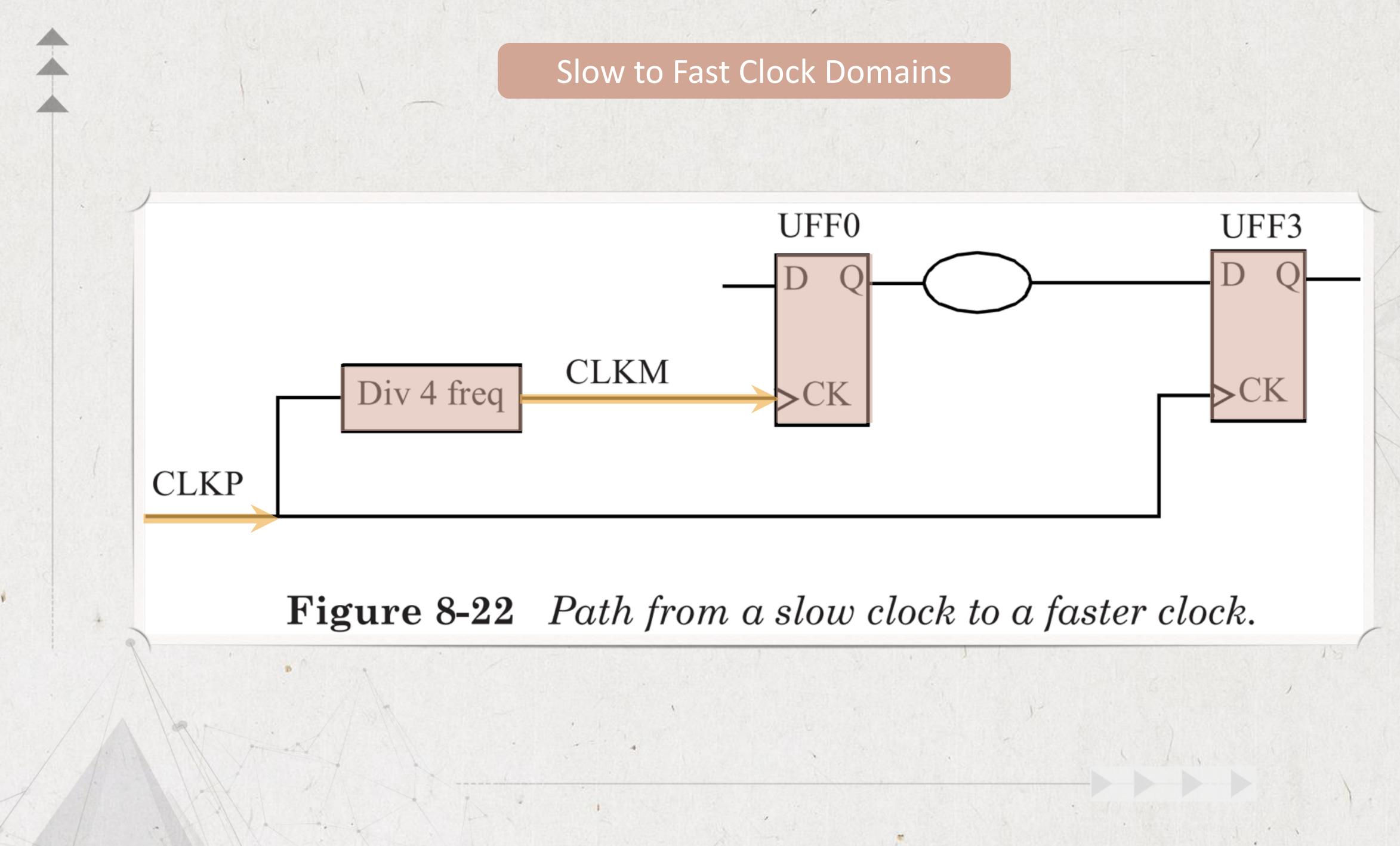

# Slow to Fast Clock Domains

**Figure 8-22** *Path from a slow clock to a faster clock.*

• When the clock frequencies are different for the launch flip-flop and the capture flip-flop, STA is performed by first determining a common base period.

• An example of a message produced when STA is performed on such a design with the above two clocks is given below.

• The faster clock is expanded so that a common period is obtained.

# Slow to Fast Clock Domains

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM) Path Group: CLKP Path Type: max

| Point                  | Incr | Path   |

|------------------------|------|--------|

|                        |      |        |

| clock CLKM (rise edge) | 0.00 | 0.00   |

| clock source latency   | 0.00 | 0.00   |

| CLKM (in)              | 0.00 | 0.00 r |

| UCKBUF0/C (CKB )       | 0.06 | 0.06 r |

| UCKBUF1/C (CKB )       | 0.06 | 0.11 r |

| UFF0/CK (DFF )         | 0.00 | 0.11 r |

| UFF0/Q (DFF ) <-       | 0.14 | 0.26 f |

| UNANDO/ZN (ND2 )       | 0.03 | 0.29 r |

| UFF3/D (DFF )          | 0.00 | 0.29 r |

| data arrival time      |      | 0.29   |

| ARIA . / PAN           |      |        |

# Endpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP)

# Notice that the launch clock is at time Ons while the capture clock is at time 5ns.

# clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF )

clock uncertainty

library setup time

data required time

data required time

data arrival time

slack (MET)

| 5.00  | 5.00 |   |

|-------|------|---|

| 0.00  | 5.00 |   |

| 0.00  | 5.00 | r |

| 0.07  | 5.07 | r |

| 0.00  | 5.07 | r |

| -0.30 | 4.77 |   |

| -0.04 | 4.72 |   |

|       | 4.72 |   |

4.72

4.44

| • | As discussed earlier, hold checks are related to the se                                                      | etup checks ar         | nd ensure that t         | he         |

|---|--------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|------------|

|   | data launched by a clock edge does not interfere wit                                                         | h the previous         | s capture. Here          | is th      |

|   | Startpoint: UFFO (rising edge-triggered<br>hold check timing report<br>Endpoint: UFF3 (rising edge-triggered | flip-flop<br>flip-flop | clocked by<br>clocked by | CLF<br>CLF |

|   | Path Group: CLKP<br>Path Type: min                                                                           |                        |                          |            |

|   | Point                                                                                                        | Incr                   | Path                     |            |

|   | clock CLKM (rise edge)                                                                                       | 0.00                   | 0.00                     | 1          |

|   | clock source latency                                                                                         | 0.00                   | 0.00                     | 1          |

|   | CLKM (in)                                                                                                    | 0.00                   | 0.00 r                   | L .        |

|   | UCKBUF0/C (CKB )                                                                                             | 0.06                   | 0.06 r                   | L .        |

|   | UCKBUF1/C (CKB )                                                                                             | 0.06                   | 0.11 r                   | L .        |

|   | UFF0/CK (DFF )                                                                                               | 0.00                   | 0.11 r                   | L          |

|   | UFF0/Q (DFF ) <-                                                                                             | 0.14                   | 0.26 r                   | L .        |

|   | UNANDO/ZN (ND2 )                                                                                             | 0.03                   | 0.29 f                   | 1          |

| 1 | UFF3/D (DFF )                                                                                                | 0.00                   | 0.29 f                   |            |

| 1 | data arrival time                                                                                            |                        | 0.29                     |            |

|   |                                                                                                              |                        |                          |            |

9.

-22

200

1.2

the LKM) LKP)

1. 1

As discussed earlier, hold checks are related to the setup checks and ensure that the • data launched by a clock edge does not interfere with the previous capture. Here is the clock CLKP (rise edge) clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF ) clock uncertainty library **hold** time data required time data required time data arrival time

slack (MET)

| 0.00 | 0.00   |

|------|--------|

| 0.00 | 0.00   |

| 0.00 | 0.00 r |

| 0.07 | 0.07 r |

| 0.00 | 0.07 r |

| 0.05 | 0.12   |

| 0.02 | 0.13   |

|      | 0.13   |

|      |        |

|      | 0.13   |

|      | -0.29  |

|      |        |

|      | 0.16   |

|      |        |

|      |        |

|      |        |

|      |        |

S. Carlos

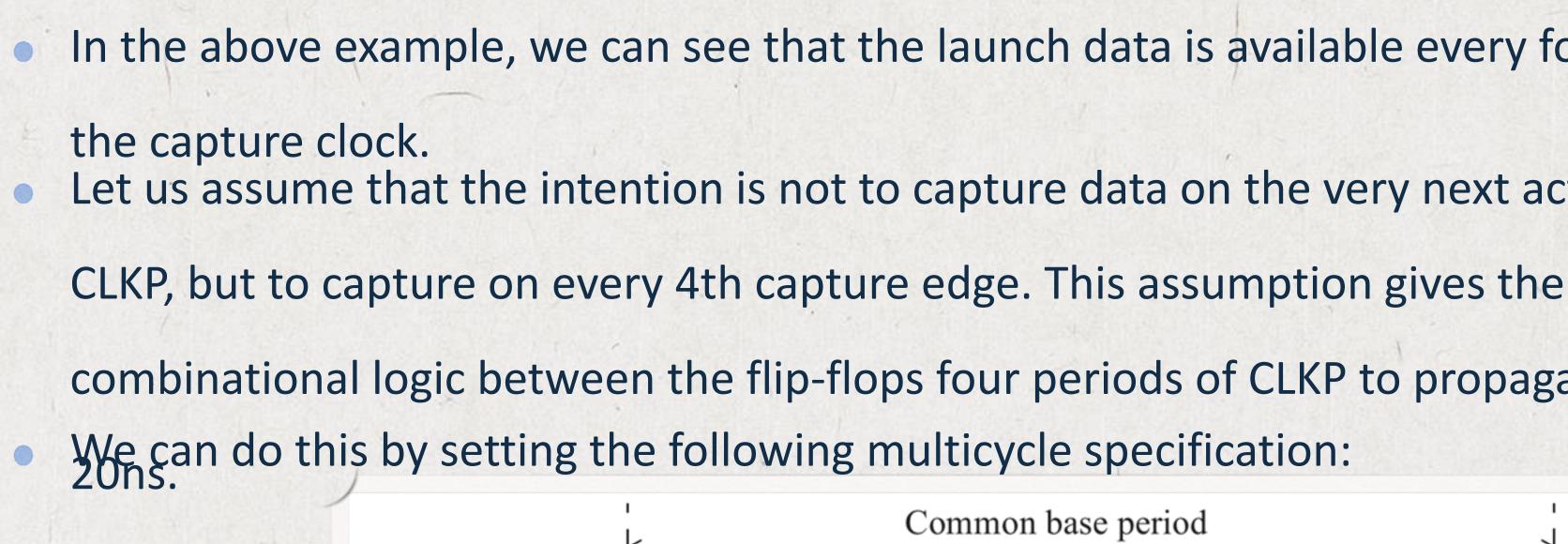

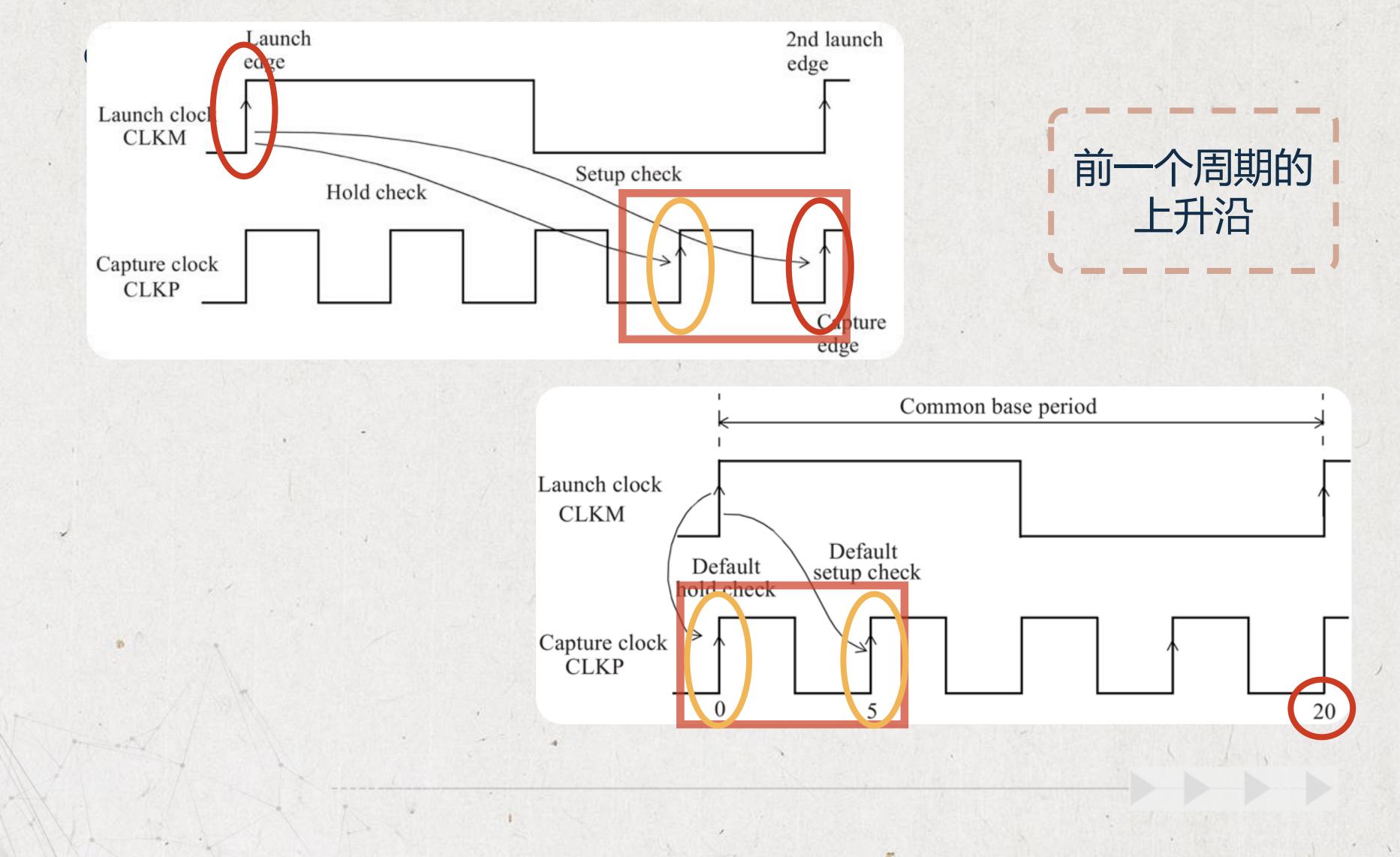

- In the above example, we can see that the launch data is available every fourth cycle of

- Let us assume that the intention is not to capture data on the very next active edge of

- combinational logic between the flip-flops four periods of CLKP to propagate, which is

• The -end specifies that the multicycle of 4 refers to the end point or the capture

clock. This multicycle specification changes the setup and hold checks to the

# Slow to Fast Clock Domains

Endpoint: UFF0 (rising edge-tri Endpoint: UFF3 (rising edge-tri Path Group: CLKP Path Type: max

Point

### clock CLKM (rise edge)

clock source latency CLKM (in) UCKBUF0/C (CKB ) UCKBUF1/C (CKB ) UFF0/CK (DFF ) UFF0/Q (DFF ) <-UNAND0/ZN (ND2 ) UFF3/D (DFF ) data arrival time

Pro and

# Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM) Endpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP)

| Incr | Path   |

|------|--------|

| 0.00 | 0.00   |

| 0.00 | 0.00   |

| 0.00 | 0.00 r |

| 0.06 | 0.06 r |

| 0.06 | 0.11 r |

| 0.00 | 0.11 r |

| 0.14 | 0.26 f |

| 0.03 | 0.29 r |

| 0.00 | 0.29 r |

|      | 0.29   |

|      |        |

# clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF )

clock uncertainty

library **setup** time

data required time

data required time data arrival time

slack (MET)

| 20.00   |

|---------|

| 20.00   |

| 20.00 r |

| 20.07 r |

| 20.07 r |

| 19.77   |

| 19.72   |

| 19.72   |

|         |

| 19.72   |

| -0.29   |

|         |

19.44

Figure shows the hold check - note that the hold check is derived from the setup check and defaults to one cycle preceding the intended capture edge. Here is the hold timing report. Notice that the hold capture edge is at 15ns, one cycle prior to the setup capture

# Slow to Fast Clock Domains

Startpoint: UFF0 (rising edge-triggered flip-flop clocked by CLKM)

Path Group: CLKP Path Type: min

Point

# clock CLKM (rise edge) clock source latency CLKM (in) UCKBUF0/C (CKB UCKBUF1/C (CKB UFF0/CK (DFF ) UFF0/Q (DFF ) <-UNANDO/ZN (ND2 UFF3/D (DFF data arrival time

# Endpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP)

| Incr     | Path   |

|----------|--------|

| <br>0.00 | 0.00   |

| 0.00     | 0.00   |

| 0.00     | 0.00 r |

| 0.06     | 0.06 r |

| 0.06     | 0.11 r |

| 0.00     | 0.11 r |

| 0.14     | 0.26 r |

| 0.03     | 0.29 f |

| 0.00     | 0.29 f |

|          | 0.29   |

# clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF )

clock uncertainty

library **hold** time

data required time

data required time

data arrival time

slack (VIOLATED)

| 15.00 | 15.00                                 |               |

|-------|---------------------------------------|---------------|

| 0.00  | 15.00                                 |               |

| 0.00  | 15.00                                 | r             |

| 0.07  | 15.07                                 | r             |

| 0.00  | 15.07                                 | r             |

| 0.05  | 15.12                                 |               |

| 0.02  | 15.13                                 |               |

|       | 15.13                                 | y is a second |

|       |                                       | · _ ·         |

|       | 15.13                                 |               |

|       | -0.29                                 |               |

|       |                                       |               |

|       | -14.84                                |               |

|       |                                       |               |

|       |                                       |               |

|       | · · · · · · · · · · · · · · · · · · · |               |

In most designs, this is not the intended check, and the hold check should be moved all the way back to where the launch edge is. We do this by setting a hold multicycle specification of 3. set multicycle path 3 -hold -from [get clocks CLKM] -to [get clocks CLKP] -end

hold check edge (one cycle before setup edge).

The cycle of 3 moves the hold checking edge back three cycles, that is, to time Ons. The distinction with a setup multicycle is that in setup, the setup capture edge moves forward by the specified number of cycles from the default setup capture edge; in a hold multicycle, the hold check edge moves backward from the default

### set\_multicycle\_path 3 -hold -from [get\_clocks CLKM] -to [get\_clocks CLKP] -end

· · · ·

• In summary, if a setup multicycle of N cycles is specified, then most likely a hold multicycle of N-1 cycles should also be specified. A good rule of thumb for multi-frequency multicycle path specification in the case of paths between slow to fast clock domains is to use the -end option. With this option, the setup and hold checks are adjusted based upon the clock cycles of the fast clock.

Slow to Fast Clock Domains

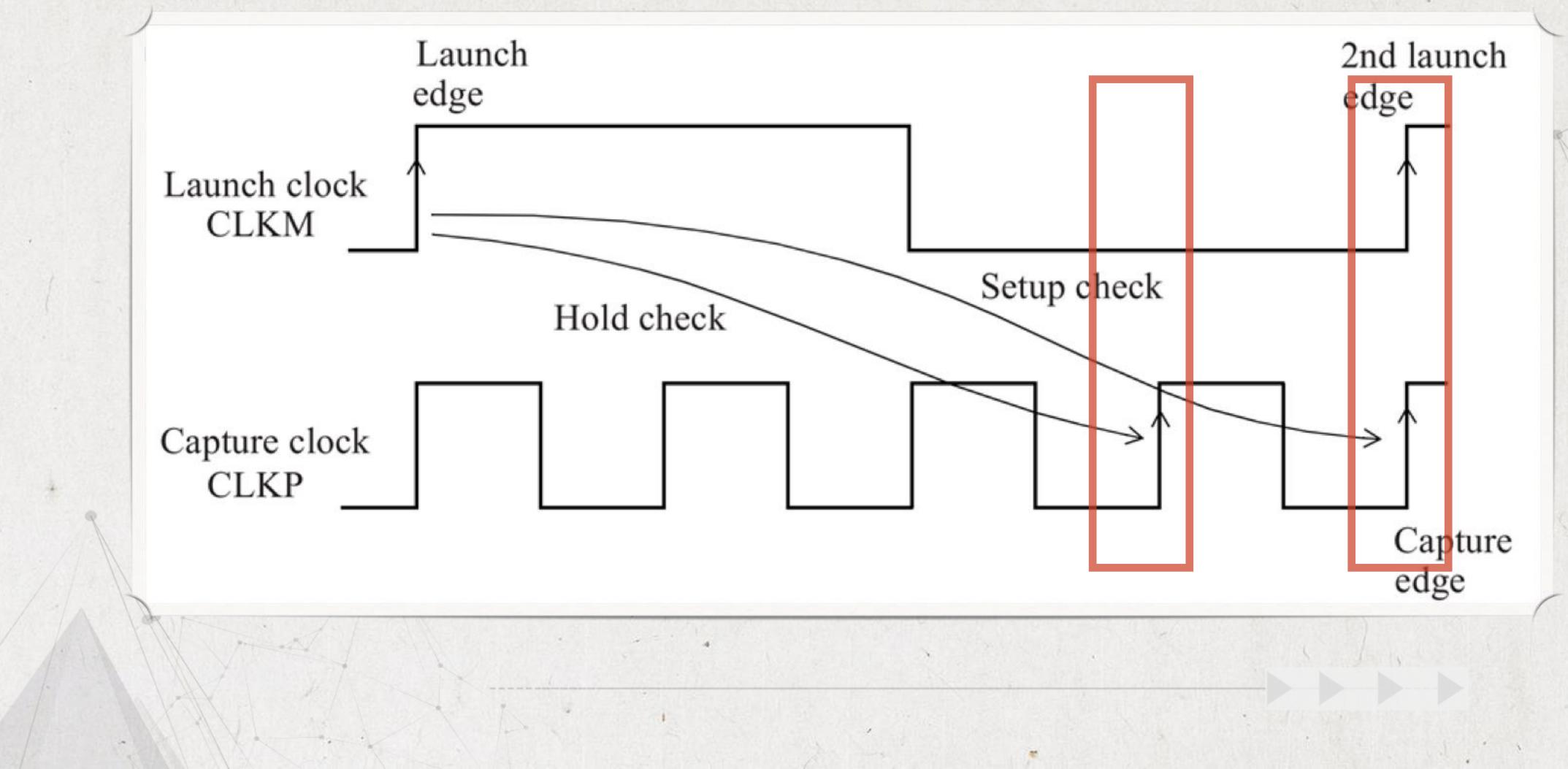

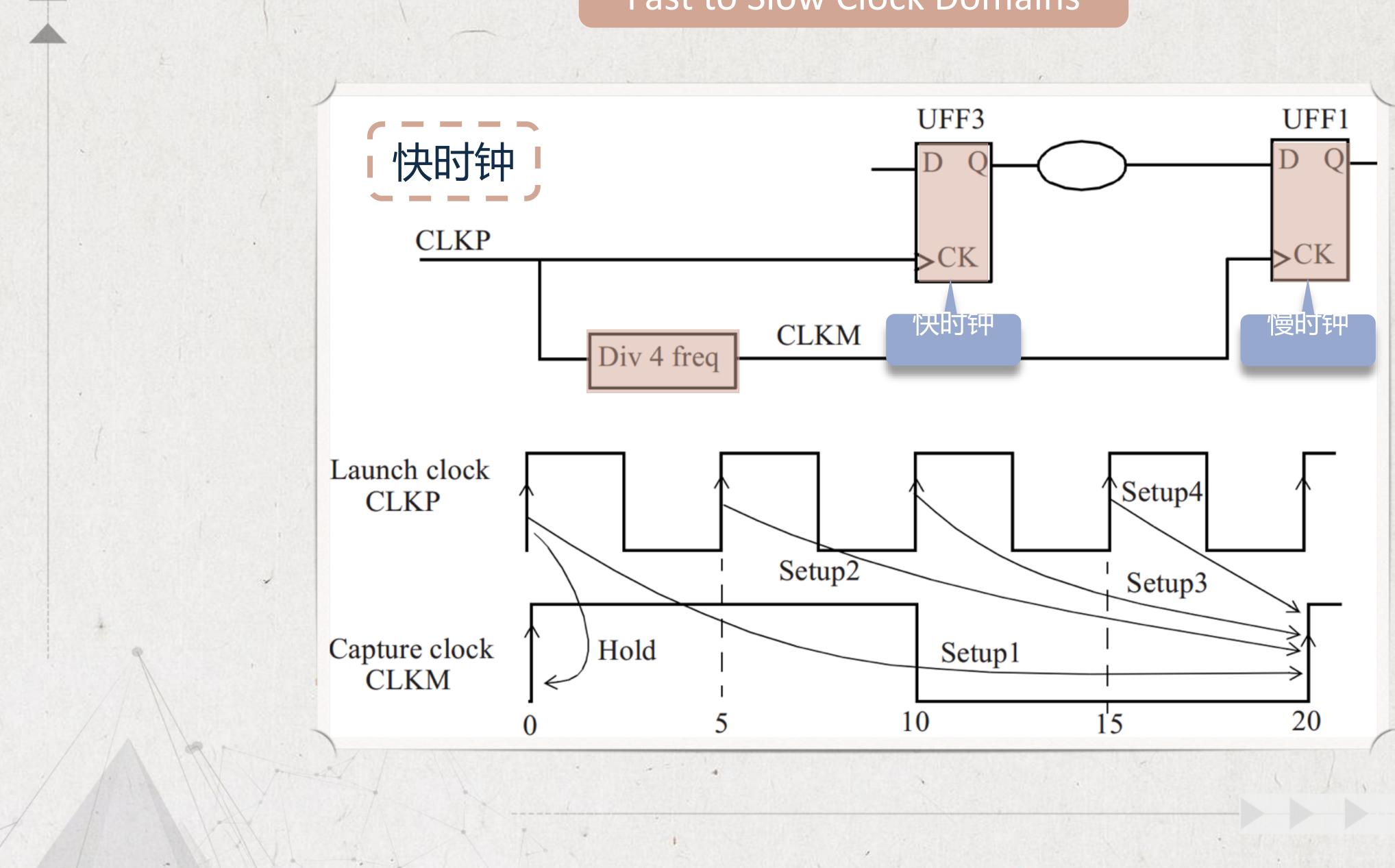

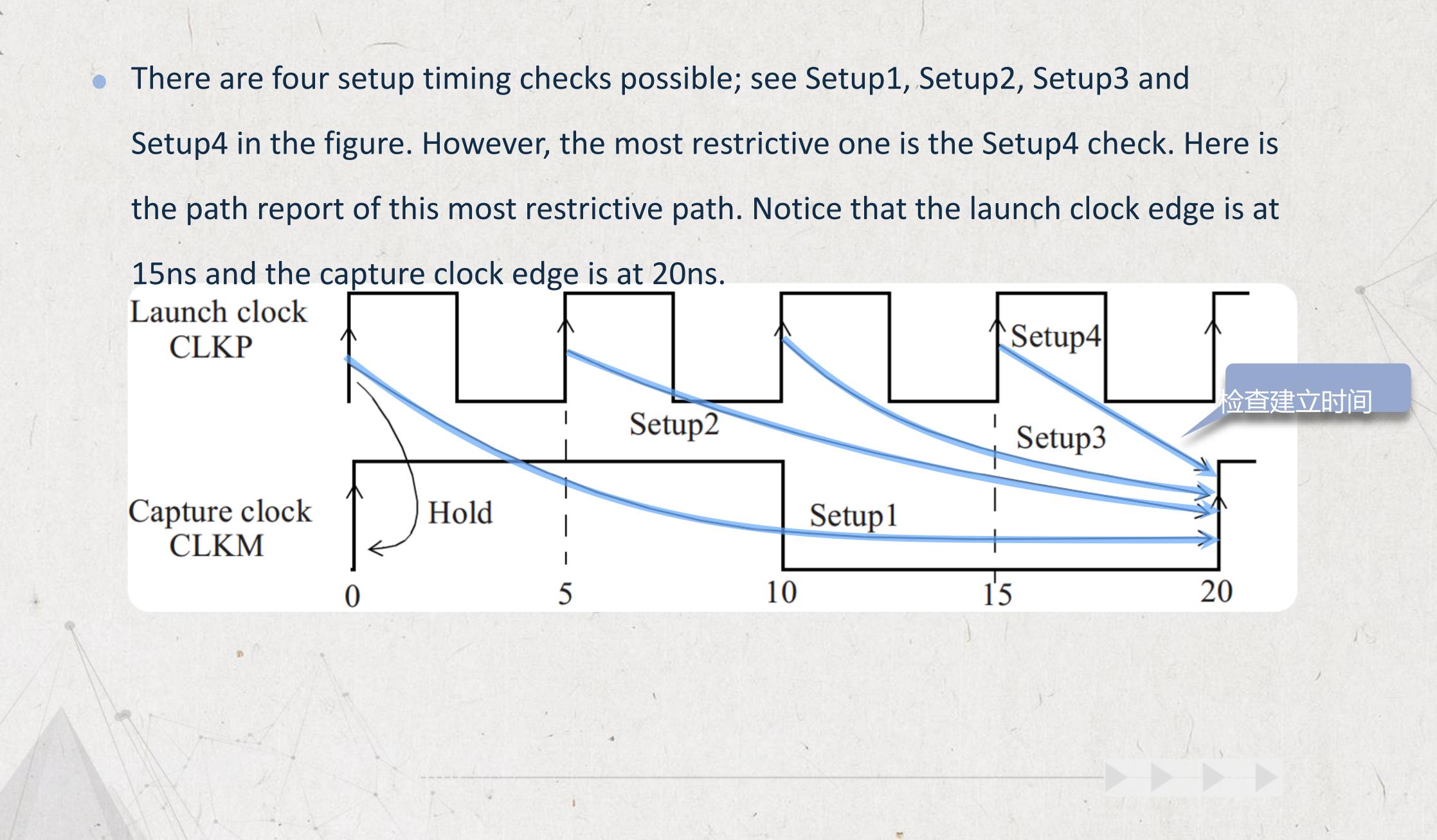

In this subsection, we consider examples where the data path goes from a fast clock domain to a slow clock domain. The default setup and hold checks are as shown in Figure when the following clock definitions are used.

# create\_clock -name CLKP -period 5 -waveform {0 2.5} [get\_ports CLKP]

# create\_clock -name CLKM -period 20 -waveform {0 10} [get\_ports CLKM]

15

1 1

Path Group: CLKM Path Type: max

Point

### clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF ) UFF3/Q (DFF ) <-UNOR0/ZN (NR2 UBUF4/Z (BUFF UFF1/D (DFF ) data arrival time

# Startpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM)

Dath

| Incr      | Path    |

|-----------|---------|

| <br>15.00 | 15.00   |

| 0.00      | 15.00   |

| 0.00      | 15.00 r |

| 0.07      | 15.07 r |

| 0.00      | 15.07 r |

| 0.15      | 15.22 f |

| 0.05      | 15.27 r |

| 0.05      | 15.32 r |

| 0.00      | 15.32 r |

|           | 15.32   |

|           |         |

Tnor

### clock CLKM (rise edge)

clock source latency CLKM (in) UCKBUF0/C (CKB ) UCKBUF2/C (CKB ) UFF1/CK (DFF ) clock uncertainty library setup time data required time data required time

data arrival time

slack (MET)

| 20.00 | 20.00   |

|-------|---------|

| 0.00  | 20.00   |

| 0.00  | 20.00 r |

| 0.06  | 20.06 r |

| 0.07  | 20.12 r |

| 0.00  | 20.12 r |

| -0.30 | 19.82   |

| -0.04 | 19.78   |

|       | 19.78   |

|       | 19.78   |

|       | -15.32  |

|       | 4.46    |

|       |         |

|       |         |

• Similar to the setup checks, there are four hold checks possible. Figure shows the most restrictive hold check which ensures that the capture edge at Ons does not capture the data being launched at Ons. Here is the timing report for this hold check.

Startpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM) Path Group: CLKM Path Type: min

Point

### clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF ) UFF3/Q (DFF ) <-UNOR0/ZN (NR2 UBUF4/Z (BUFF UFF1/D (DFF ) data arrival time

| Incr     | Path   |  |

|----------|--------|--|

| <br>0.00 | 0.00   |  |

| 0.00     | 0.00   |  |

| 0.00     | 0.00 r |  |

| 0.07     | 0.07 r |  |

| 0.00     | 0.07 r |  |

| 0.16     | 0.22 r |  |

| 0.02     | 0.25 f |  |

| 0.06     | 0.30 f |  |

| 0.00     | 0.30 f |  |

|          | 0.30   |  |

|          |        |  |

# clock CLKM (rise edge)

clock source latency CLKM (in) UCKBUF0/C (CKB ) UCKBUF2/C (CKB ) UFF1/CK (DFF ) clock uncertainty library hold time data required time

data required time

data arrival time

slack (MET)

| 0.00 | 0.00  |    |

|------|-------|----|

| 0.00 | 0.00  |    |

| 0.00 | 0.00  | r  |

| 0.06 | 0.06  | r  |

| 0.07 | 0.12  | r  |

| 0.00 | 0.12  | r  |

| 0.05 | 0.17  |    |

| 0.01 | 0.19  |    |

|      | 0.19  |    |

|      |       |    |

|      | 0.19  |    |

|      | -0.30 |    |

|      |       |    |

|      | 0.12  |    |

|      |       |    |

|      |       |    |

|      |       | .) |

• In general, a designer may specify the data path from the fast clock to the slow clock to be a multicycle path. If the setup check is relaxed to provide two cycles of the faster clock for the data path, the following is included for this multicycle specification:

The -start option refers to the launch clock and is the default for a multicycle hold.

# set multicycle path 2 -setup -from [get clocks CLKP] -to [get clocks CLKM] -start

# set multicycle path 1 -hold -from [get clocks CLKP] -to [get clocks CLKM] -start

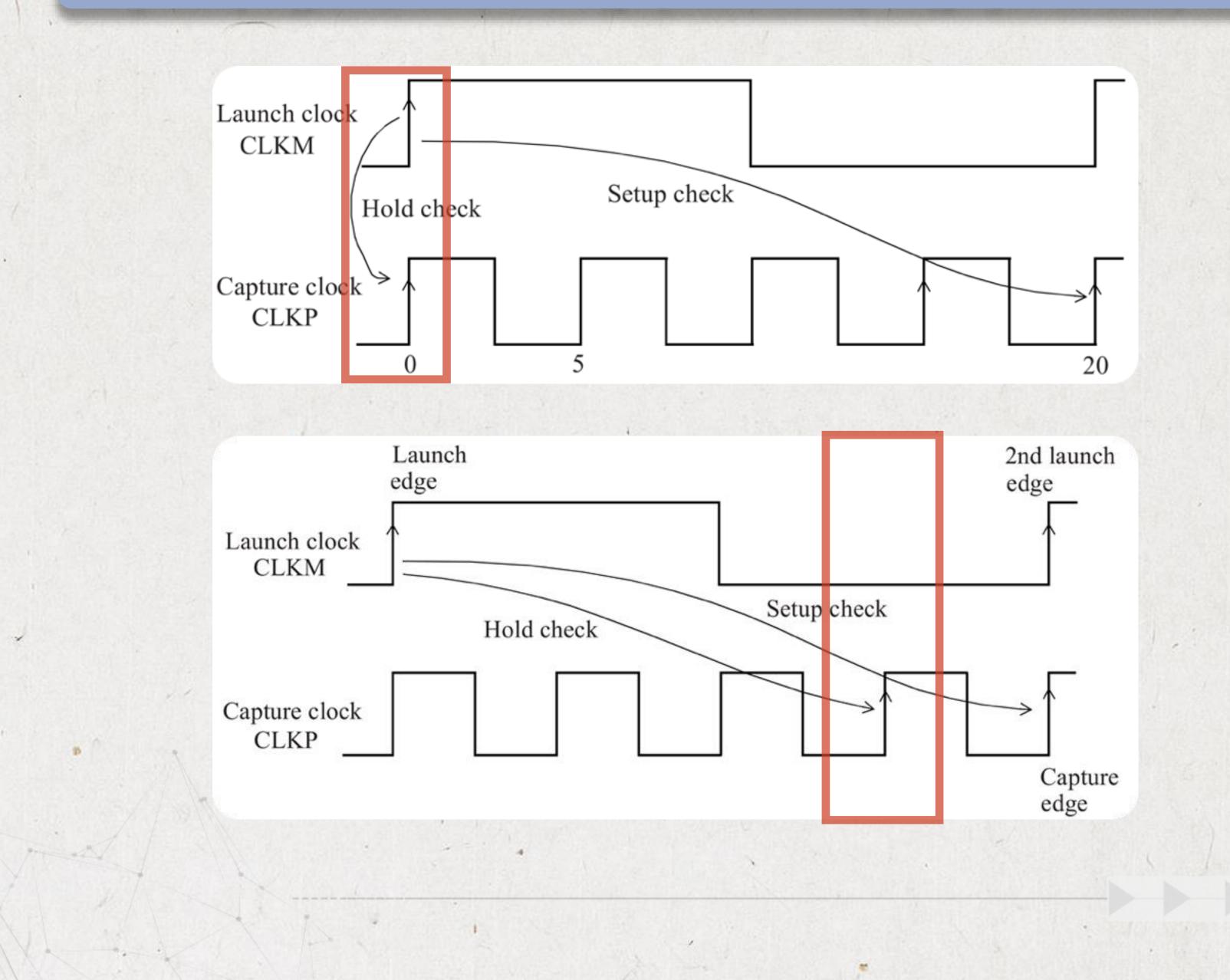

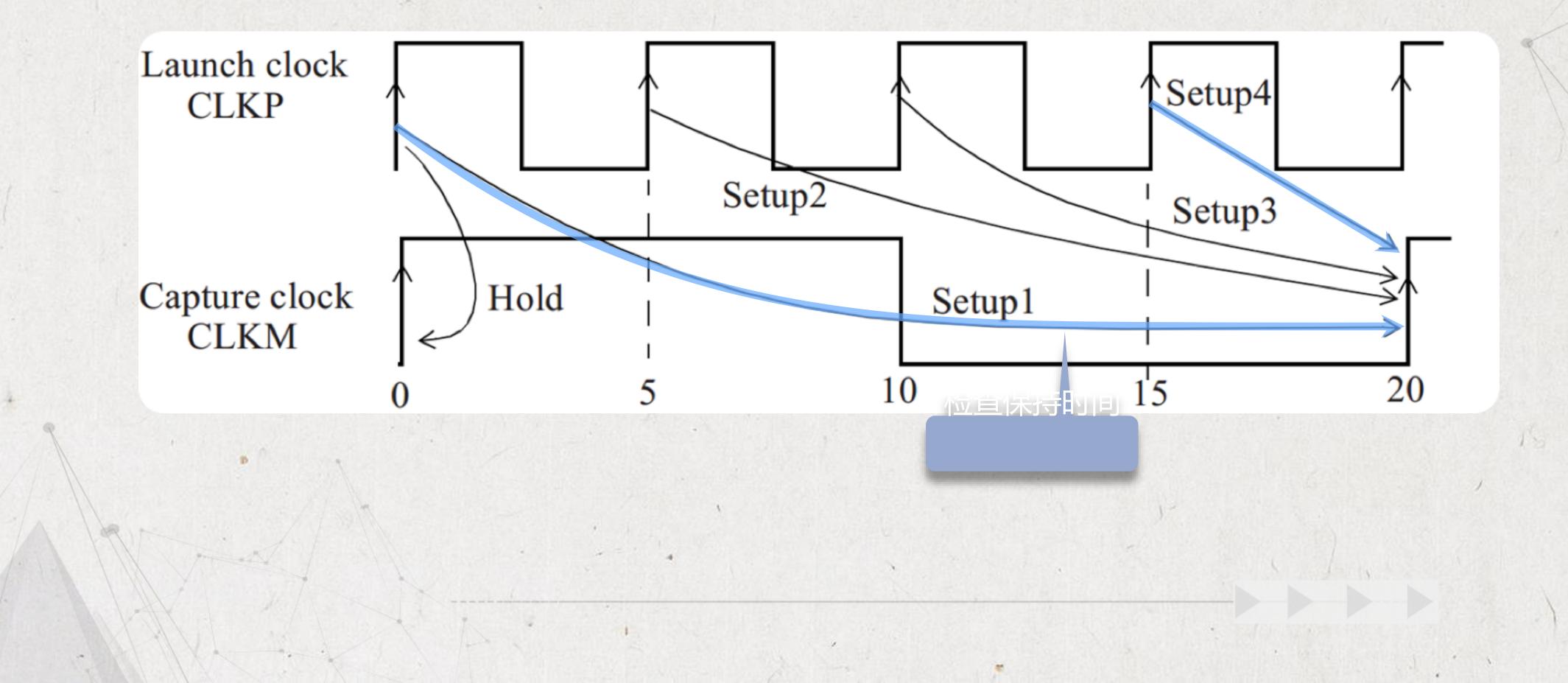

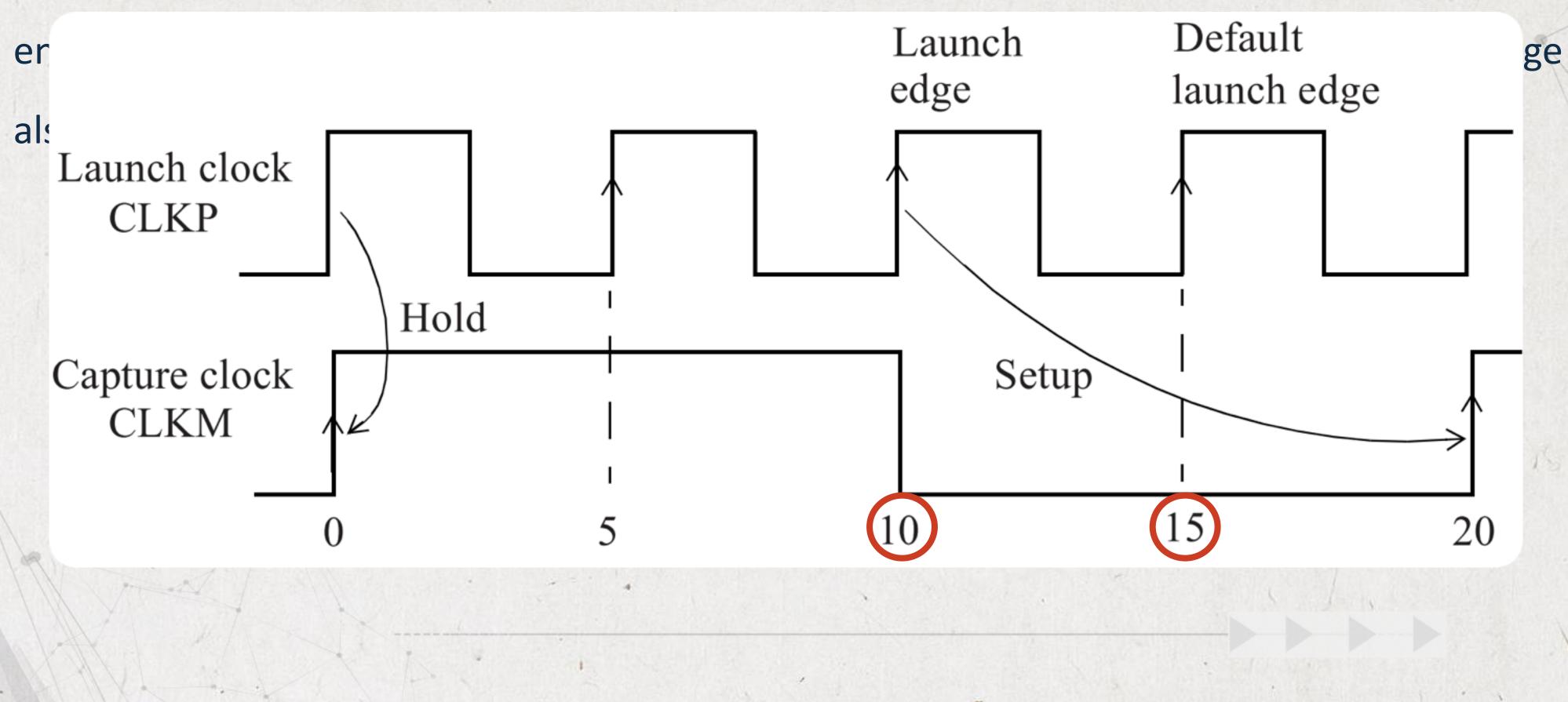

In this case, Figure shows the clock edges used for the setup and hold checks. The -start option specifies that the unit for the number of cycles (2 in this case) is that of the launch clock (CLKP in this case). The setup multicycle of 2 moves the launch edge one edge prior to the default launch edge, that is, at 10ns instead of the default 15ns. The hold multicycle

## • Here is the setup path report. As expected, the launch clock edge is at 10ns

and the capture clock edge is at 20ns. Startpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by CLKM) Path Group: CLKM Path Type: max

Point

# clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF ) UFF3/Q (DFF ) <-UNOR0/ZN (NR2 ) UBUF4/Z (BUFF ) UFF1/D (DFF ) data arrival time

| Incr  | Path    |  |

|-------|---------|--|

|       |         |  |

| 10.00 | 10.00   |  |

| 0.00  | 10.00   |  |

| 0.00  | 10.00 r |  |

| 0.07  | 10.07 r |  |

| 0.00  | 10.07 r |  |

| 0.15  | 10.22 f |  |

| 0.05  | 10.27 r |  |

| 0.05  | 10.32 r |  |

| 0.00  | 10.32 r |  |

|       | 10.32   |  |

|       |         |  |

• Here is the setup path report. As expected, the launch clock edge is at 10ns

### and the capture clock edge is at 20ns. clock CLKM (rise edge)

clock source latency CLKM (in) UCKBUF0/C (CKB UCKBUF2/C (CKB UFF1/CK (DFF ) clock uncertainty library **setup** time data required time

data required time data arrival time

slack (MET)

|    | Phone Party and |        | 146.25 |

|----|-----------------|--------|--------|

| 20 | .00             | 20.00  |        |

| 0  | .00             | 20.00  |        |

| 0  | .00             | 20.00  | r      |

| 0  | .06             | 20.06  | r      |

| 0  | .07             | 20.12  | r      |

| 0  | .00             | 20.12  | r      |

| -0 | .30             | 19.82  |        |

| -0 | .04             | 19.78  |        |

|    |                 | 19.78  |        |

|    |                 |        |        |

|    |                 | 19.78  |        |

|    |                 | -10.32 |        |

|    |                 |        |        |

|    |                 | 9.46   |        |

|    | -               |        |        |

|    |                 |        |        |

# • Here is the hold path timing report. The hold check is at Ons where both the

ature and laurada ala ala barra risina adaa Startpoint: UFF3 (rising edge-triggered flip-flop clocked by CLKP) Endpoint: UFF1 (rising edge-triggered flip-flop clocked by **CLKM**) Path Group: CLKM Path Type: min

Point

### clock CLKP (rise edge)

clock source latency CLKP (in) UCKBUF4/C (CKB ) UFF3/CK (DFF ) UFF3/Q (DFF ) <-UNOR0/ZN (NR2 UBUF4/Z (BUFF) UFF1/D (DFF data arrival time

| Incr | Path   |   |

|------|--------|---|

|      |        | - |

| 0.00 | 0.00   |   |

| 0.00 | 0.00   |   |

| 0.00 | 0.00 r |   |

| 0.07 | 0.07 r |   |

| 0.00 | 0.07 r |   |

| 0.16 | 0.22 r |   |

| 0.02 | 0.25 f |   |

| 0.06 | 0.30 f |   |

| 0.00 | 0.30 f |   |

|      | 0.30   |   |

|      |        |   |

# • Here is the hold path timing report. The hold check is at Ons where both the

1

### canture and launch clocks have rising clock CLKM (rise edge)

clock source latency

CLKM (in)

UCKBUF0/C (CKB )

UCKBUF2/C (CKB )

UFF1/CK (DFF ) clock uncertainty library **hold** time data required time

data required time data arrival time

slack (MET)

| a eques |      | )     |   |

|---------|------|-------|---|

|         | 0.00 | 0.00  |   |

|         | 0.00 | 0.00  |   |

|         | 0.00 | 0.00  | r |

|         | 0.06 | 0.06  | r |

|         | 0.07 | 0.12  | r |

|         | 0.00 | 0.12  | r |

|         | 0.05 | 0.17  |   |

|         | 0.01 | 0.19  |   |

|         |      | 0.19  |   |

|         |      |       |   |

|         |      | 0.19  |   |

|         |      | -0.30 |   |

|         |      |       |   |

|         |      | 0.12  |   |

|         |      |       |   |

|         |      |       |   |

|         |      |       |   |

A 64 14

1 1 1

Unlike the case of paths from slow to fast clock domains, a good rule of thumb for multi-frequency multicycle path specification in the case of paths from fast to slow clock domains is to use the -start option.

The setup and hold checks are then adjusted based upon the fast clock.