## 数字集成电路静态时序分析基础

邸志雄 博士, zxdi@home.swjtu.edu.cn

西南交通大学信息科学与技术学院

## Part-1:TCL语言

01 > TCL在EDA工具中的扩展与应用

02 > 使用TCL控制EDA工具流程

Tcl = **T**ool **C**ommand **L**anguage

A simple programming language.

Open, industry standard.

Many Synopsys tools' command interfaces are based on the Tcl command language.

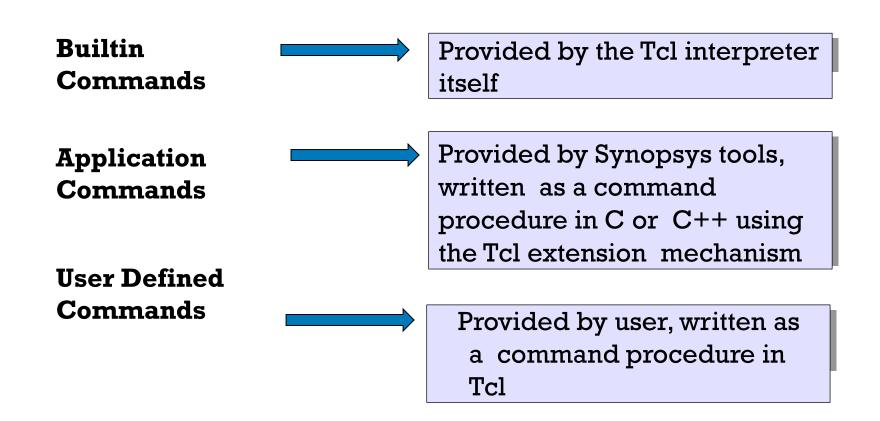

#### **Tcl Scripts are Based on Commands**

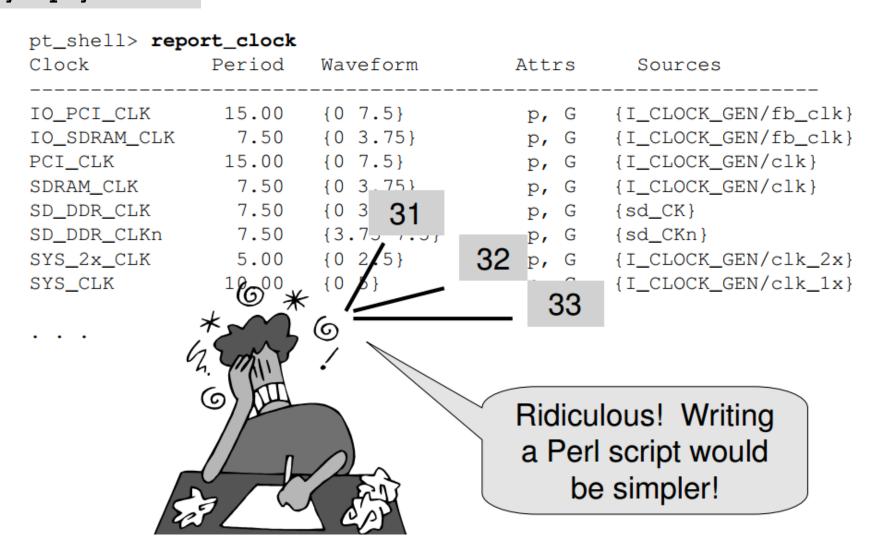

Example: Why Synopsys TCL?

How many clocks have been defined for this design?

Suggest a report that will list all clocks?

#### TCL的应用

#### Example: Why Synopsys TCL?

Example: Why Synopsys TCL?

## sizeof\_collection [all\_clocks]

€ 52

Powerful

Flexible

Easy

## References:

- Using Tcl with Synopsys Tools

- **PrimeTime User Guide: Fundamentals:**

- PrimeTime User Guide: Advanced Timing Analysis

01 > TCL在EDA工具中的扩展与应用

02 > 使用TCL控制EDA工具流程

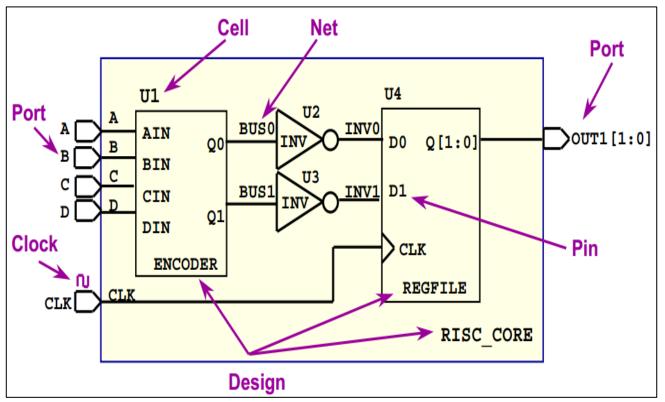

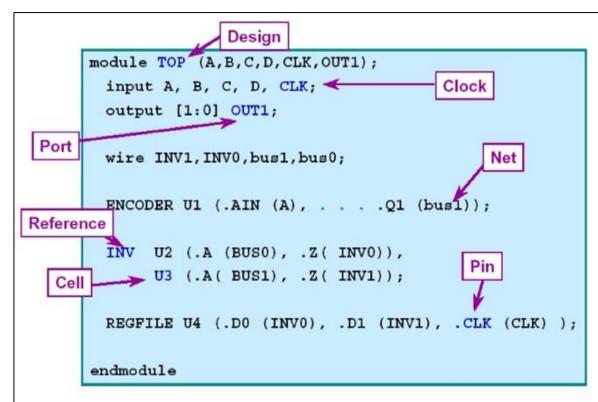

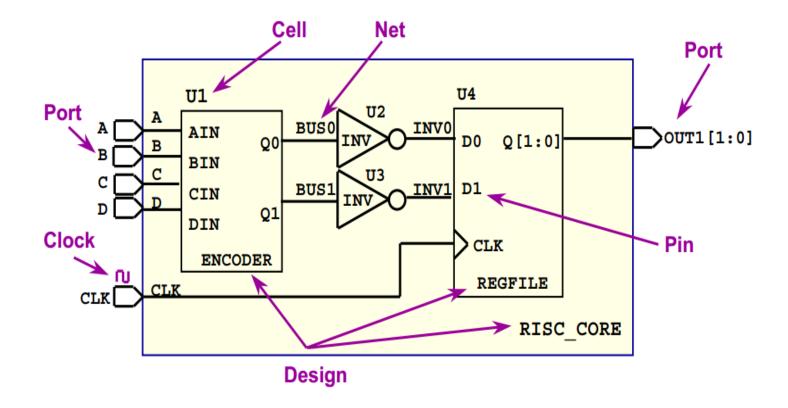

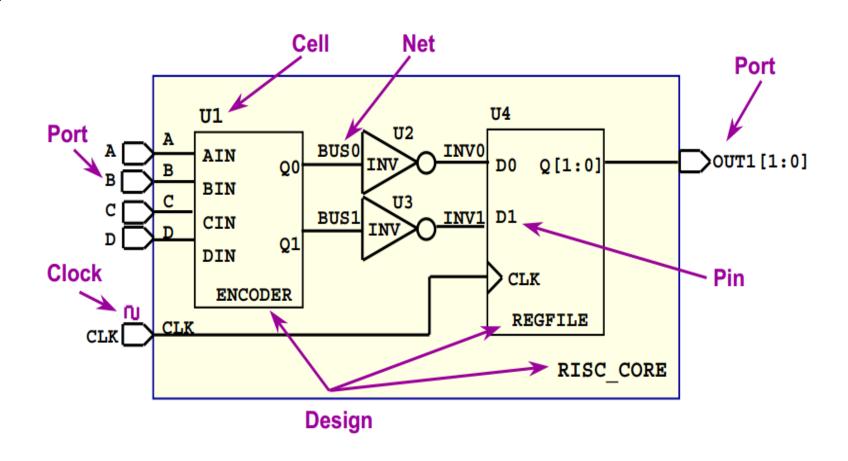

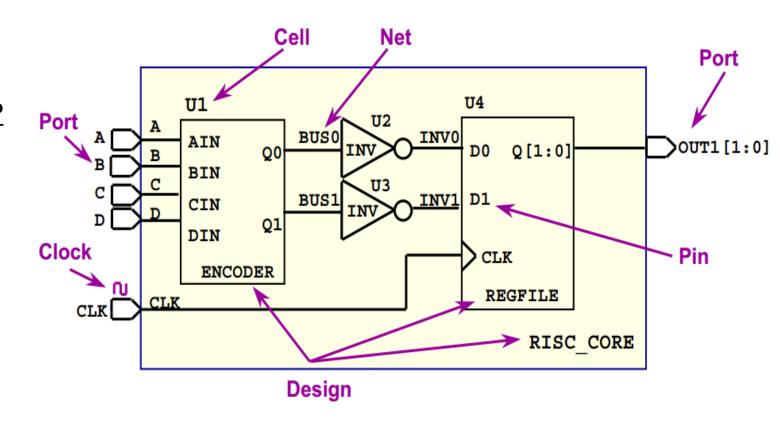

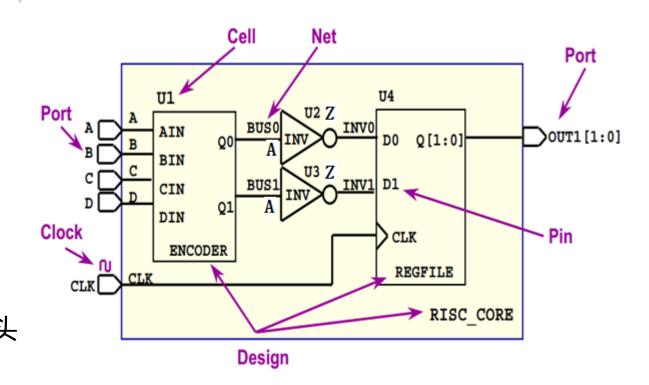

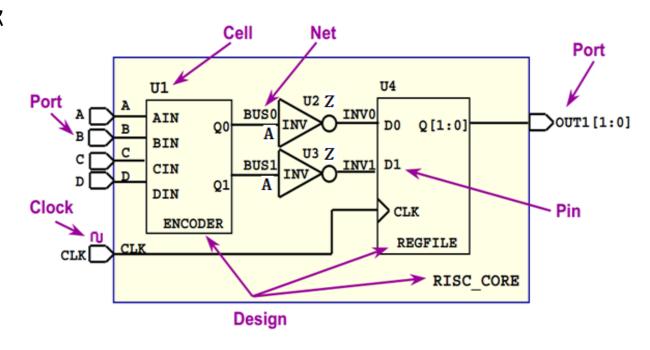

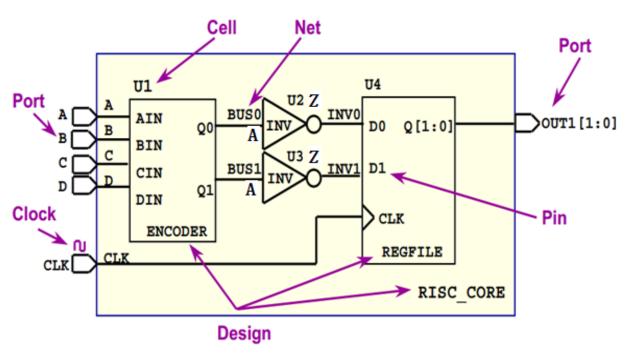

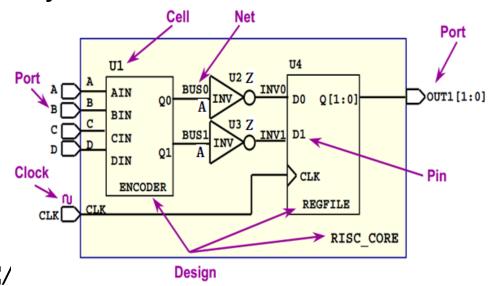

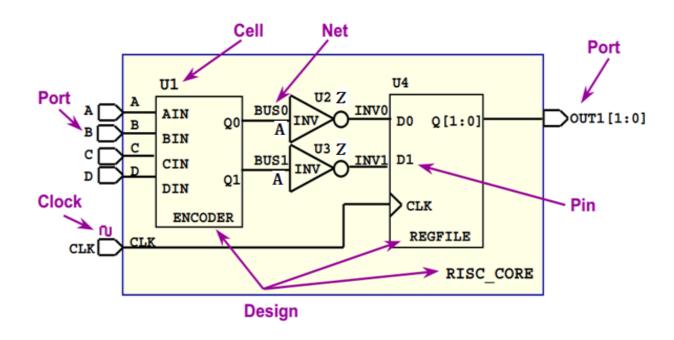

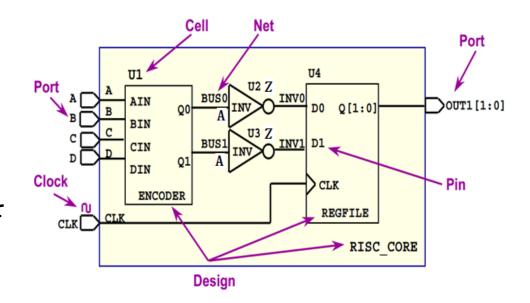

#### TCL的应用: Design Object

通过对Design Object的分析,我们来了解和学习DC获取电路并进行解析的方法。

Schematic View and Code of Design Objects

语法格式: get\_ports portsName

指令功能:返回design中对应的ports object

例-1:如何查看design当中有没有一个port叫做CLK?

Shell> get\_ports CLK {CLK}

例-2: 我们想查看design当中有没有一个port叫做SPI?

Shell> get\_ports SPI

No object Found!

例-3: 我们想查看design当中所有的port (\*可以通配任何字符)

Shell> get\_ports \* Cell Net **Port** {A B C D CLK OUT[0] OUT[1]} U4 U1 **Port** U2 BUS 0 NV0 AIN OUT1[1:0] Q[1:0] Q0 BIN BUS1 NV1 D1 CIN Q1 DIN Clock Pin CLK **ENCODER** REGFILE CLK RISC CORE Design

例-4: 假设我们有port名字叫 {CLKA CLKB OUTA OUTB INA INB}

如果我们想得到所有C开头的port 怎么做?

Shell> get\_ports C\*

{CLKA CLKB}

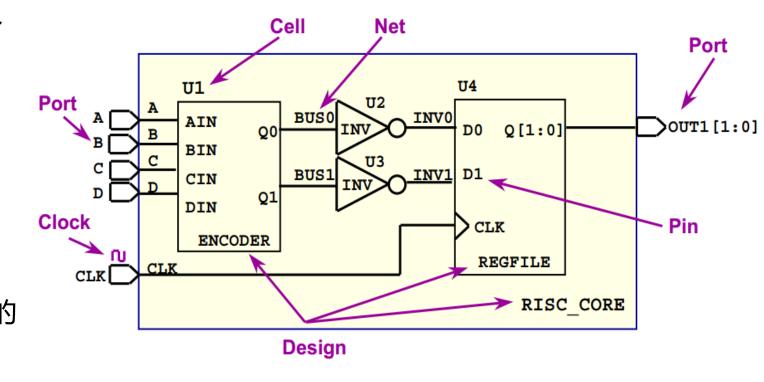

语法格式: get\_cells cellsName

指令功能:返回design中对应的cell的instance

name object

#### 回顾几个概念:

□ 什么是reference name(ref\_name)?

{ENCODER INV REGFILE}

□ <u>什么是instance name?</u>

{U1 U2 U3 U4}

举例-1: 我们想查看design当中有没有一个cell叫做U4? Shell> get\_cells U4 {U4}

举例-2: 我们想查看design当中所有的cell Shell> get\_cells \* {U1 U2 U3 U4}

举例-3: 我们想查看design当中以3为结尾的 cells Shell> get\_cells \*3

{U3}

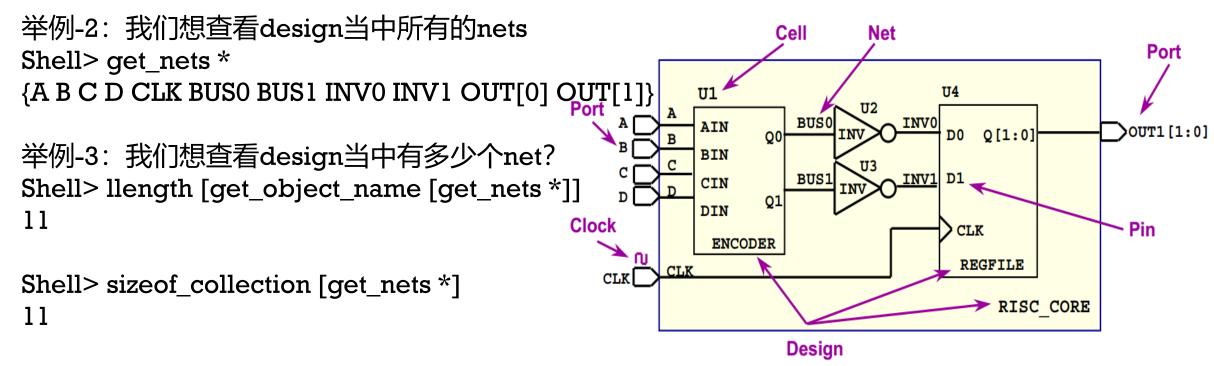

语法格式: get\_nets netsName

指令功能:返回design中net的

object

举例-1: 查看design当中有没有一个net以INV

开头?

Shell> get\_nets INV\*

{INV0 INV1}

注意两条指令的区别噢!

语法格式: get\_pins pinsName

指令功能:返回design中pin的object

举例-1: 查看design当中有哪些pin的名字叫做Z? Shell> get\_pins \*/Z {INV0/Z INV1/Z}

举例-2: 查看design当中有哪些pin的名字以Q开头?

Shell> get\_pins \*/Q\*

{ENCODER/Q0 ENCODER/Q1 REGFILE/Q[1]

REGFILE/Q[0]}

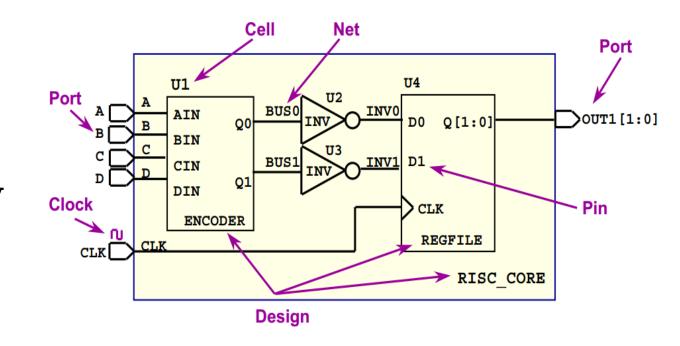

"数据类型: object (对象)"与其"属性"

#### 说明:

- □ object是对于tcl脚本一个重要的扩展;

- □ 常见的对象有四种 cell, net, port, pin;

- □ 每种object有它的属性。

下面的ppt将介绍一些常见属性。

- □任何一个属性都可以用get\_attribute得到,

- □ list\_attribute -class \* 可以得到所有object 的属性,

- □ 部分属性可以用set\_attribute来设置。

"数据类型: object (对象)"与其"属性"

#### Cell object

属性 ref\_name: 用来保存其map到的reference cell名称 Shell> get\_attribute [get\_cells -h U3] ref\_name {INV}

#### Pin object:

属性 owner\_net:用来保存与之相连的net的名称 Shell> get\_attribute [get\_pins U2/A] owner\_net {BUS0}

#### Port object:

属性 direction: 用来保存port 的方向

Shell> get\_attribute [get\_ports A] direction

{in}

Shell> get\_attribute [get\_ports OUT[1]] direction Port

{out}

#### > Net object:

属性 full\_name:用来保存net的名称

Shell> get\_attribute [get\_nets INV0] full\_name {INV0}

Shell> get\_object\_name [get\_nets INV0] {INV0}

\*Shell> get\_attribute INV0 full\_name

Error: No attribute found

#### 理解了属性,就能做更多的事情啦:

```

get_* -f:

-f 这个option可以用来过滤属性,以得到我们想要的object

```

#### 例子-1:

想得到所有方向是input的port Shell> get\_ports \* -f "direction==in" {A B C D CLK}

#### 例子-2:

想得到所有方向是output的pin Shell>get\_pins \* -f "direction ==out" {U1/Q0 U1/Q1 U2/Z U3/Z REGFILE/Q[0] REGFILE/

#### 例子-3:

想得到所有ref\_name 是INV的 cell Shell>get\_cells \* -f "ref\_name == INV" {U2 U3}

#### 另外一个最关键的option

```

get_* [object]-of:

-of 这个option可以用来得到与你指定object相连接的object

```

#### object的连接关系:

```

--port object <-> net object

>get_nets -of [get_port A]

A

```

- --net object <-> port object / pin object

> get\_net -of [get\_pin U2/A]

BUS0

- --pin object <-> net object

> get\_pin -of [get\_net INV1]

U3/Z

- --cell object <-> pin object

>get\_pins -of [get\_cell U4]

{U4/D0 U4/D1 REGFILE/Q1 REGFILE/Q2}

#### 练习:

假定我们想得到电路中所有的inverter,那么应该输入什么样的脚本呢?

#### 解答:

- (1) 直接使用Synopsys TCL指令: get\_buffers -inverter

- (2) 人工扩展TCL指令: get\_inverters

人工扩展TCL指令: get\_inverters

#### 解题思路:

- (1) 使用get\_lib\_cells 得到所有引脚总数为2的cell set lcells [filter\_collection [get\_lib\_cells -quiet [get\_attr \$lib extended\_name]/\*] "number\_of\_pins==2 && base\_name=~\${pattern}"]

- (2) 使用foreach\_in\_collection, 循环检测每一个cell。

- (3) 对于每一个cell, 使用-filter 得到输入引脚、输出引脚的全名,以及功能名称。 set opin [get\_lib\_pins -quiet -of\_object \${lcell} -filter "pin\_direction==out"] set ipin [get\_lib\_pins -quiet -of\_object \${lcell} -filter "pin\_direction==in"] set opin\_name [get\_attribute -quiet \${opin} base\_name] set ipin\_name [get\_attribute -quiet \${ipin} base\_name] set cell\_func [get\_attribute -quiet \${opin} function]

- (4) 输入引脚和输出引脚数量都为1, 且功能为反相器, 则就是我们想要的cell

- (5) 循环执行第(1) 执行的步骤, 最终可获得所有的反相器

01 > TCL在EDA工具中的扩展与应用

02 > 使用TCL控制EDA工具流程

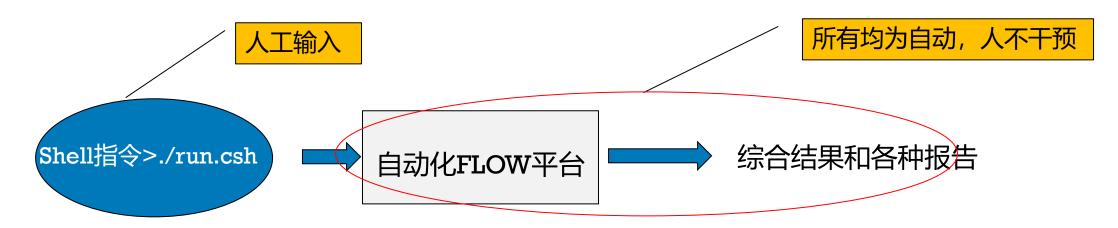

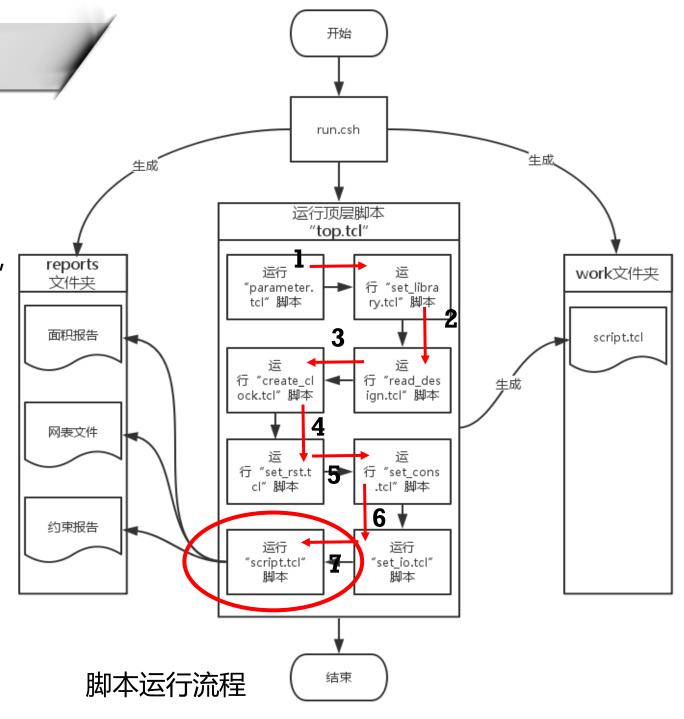

讲述一个简单的、入门级的Synopsys DesignComplier自动化方案,供初学者参考,感兴趣的同学对该方案进行优化和升级。

#### 特点:

- □该过程无需人为操作,用户只需要输入一条shell启动指令就能完全自动化的完成整个综合过程。

- □ 具备普适性和可重用性。在综合不同的设计时,只需要修改参数配置文件中的环境变量,不需要修改制本。

自动化电路综合平台只需用户将待综合的设计和库文件放入一个文件夹,修改与待综合设计对象有关的环境变量参数,在命令窗口唤醒DC的指令,即自动化地完成综合过程,并得到综合后的网表文件和所需的报告。

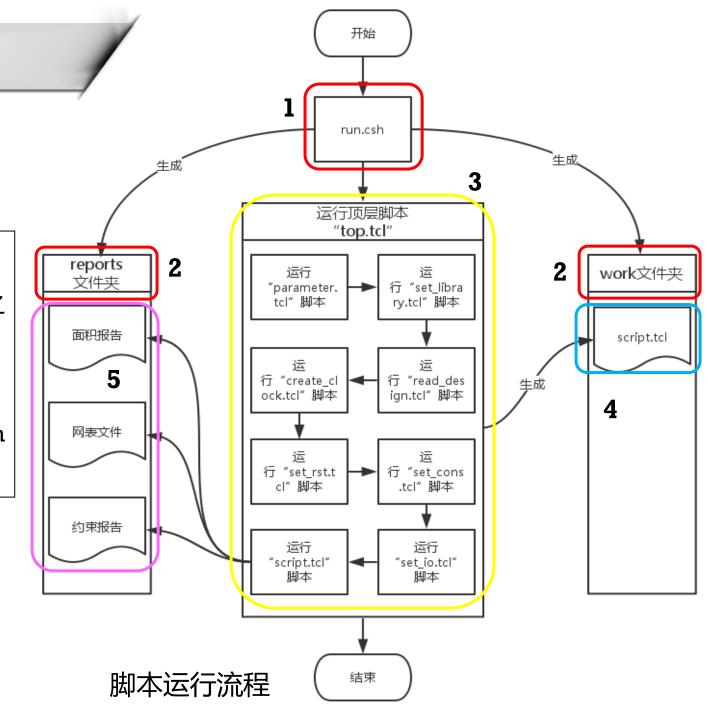

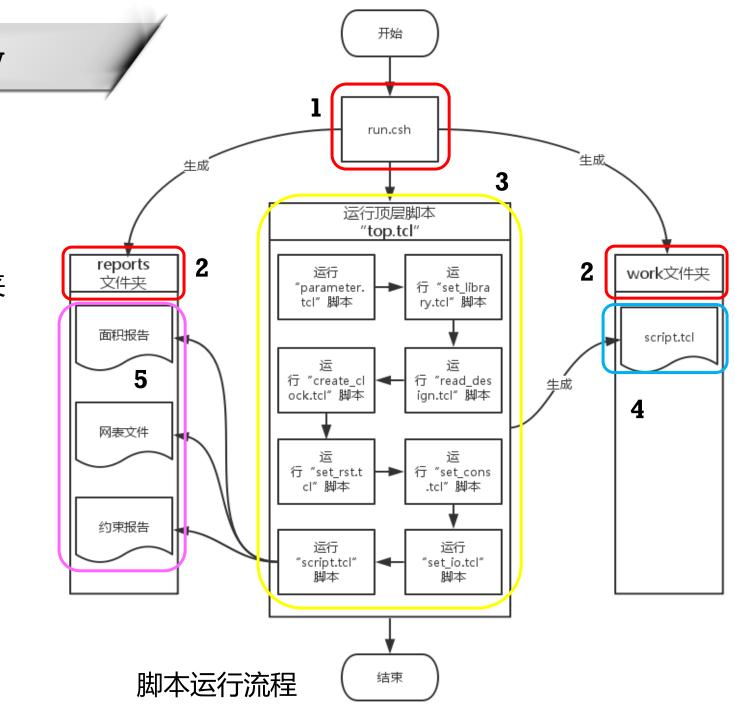

#### 运行流程:

① 运行run.csh脚本,启动DC

#!/bin/csh-f

\rm -rf \*.log \*.svf alib\* reports log work #清除之

前的文档

mkdir reports work #新建文件夹

dc\_shell-xg-t -32bit -f ./top.tcl #启动Design

Compiler并运行top.tcl

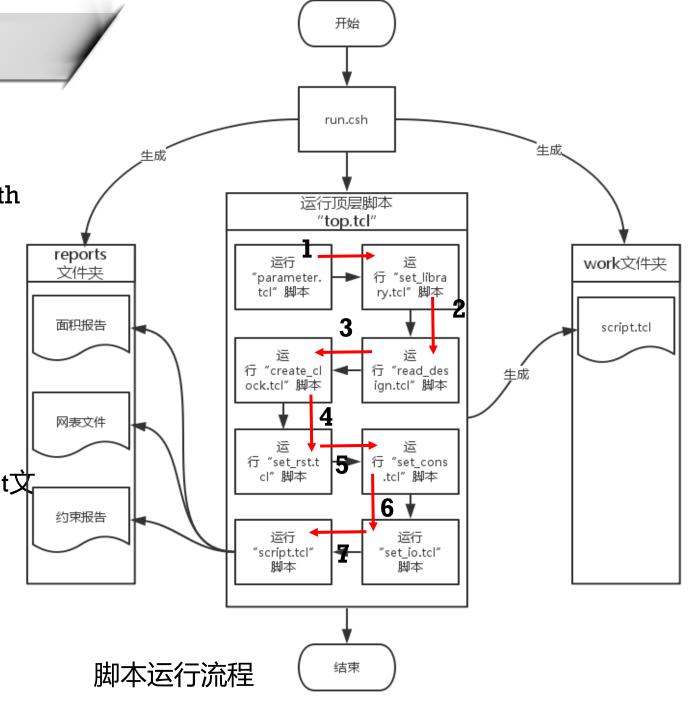

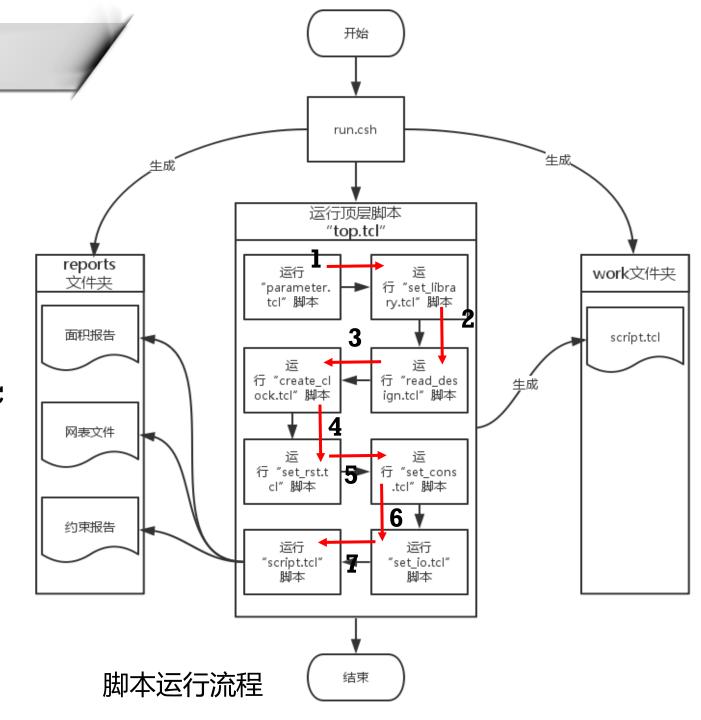

#### 运行流程:

- ① 运行run.csh脚本, 启动DC

- ② 建立reports与work两个文件夹。reports 文件夹用于存放生成的报告,work文件夹用于存放该平台运行过程中生成的文档、脚本。

- ③ 启动顶层脚本top.tcl文件;

- ④ top.tcl按先后顺序启动各个子脚本,最终 生成script.tcl;

- ⑤ DC读取script.tcl中的约束,最终完成综合,并将所有报告写入reports文件夹中。

## top.tcl脚本运行机制:

l、set\_library.tcl: 生成设定库文件和search path

的约束

2、read\_design.tcl: 生成读入设计文件的约束

3、create\_clock.tcl: 生成时钟源相关的约束

4、set\_rst.tcl: 生成复位端口约束的约束

5、set\_io.tcl:生成输入输出端口的约束

6、set\_cons.tcl: 生成保存门级网表、各种reprot文

件的约束

## 注意:

- 1、以上所有约束都自动生成,无需人为干预;

- 2、库文件、代码、时钟、复位、输入输出等均 根据代码自动进行匹配,并生成相应的约束;

- 3、最终所有的约束都被写入script.tcl中,供DC 读取,完成最终的逻辑综合过程。

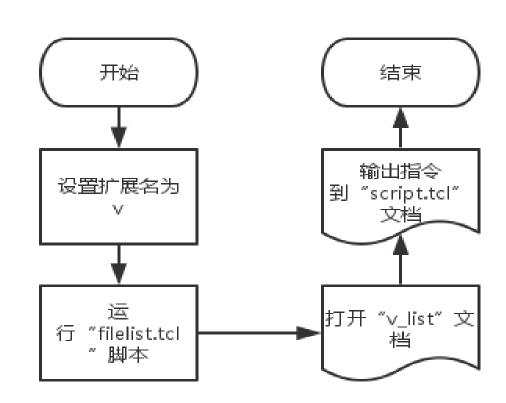

▶ 重要的脚本子模块——代码读入约束生成

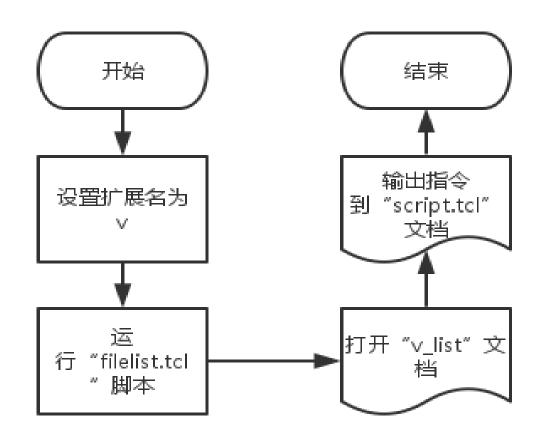

#### 工作流程:

- ① 设计文件通常使用verilog语言,所以扩展名通常为v, 所以先将变量extension设为v;

- ② 调用filelist.tcl脚本, filelist.tcl脚本会将所有扩展 名为v的文件的文件路径输出到一个名为v\_list的 文档。

- ③ 打开v\_list文档,根据文件的内容将读入设计文件的指令输出到script.tcl脚本。

#### 脚本运行流程

▶ 重要的脚本子模块——代码读入约束生成

```

set extension v

source [file join $::script_path test/filelist.tcl]

#调用filelist.tcl脚本

set des [open [file join $::script_path test/work/v_list] r]

set design [gets $des] #打开v_list文档

for {} {$design!=""} {set design [gets $des]} {

puts $script [format "read_file -format verilog %s"

$design]

#输出读入设计文件指令

puts $script [format "current_design %s" $top]

#输出设置顶层设计指令

```

脚本运行流程

➤ 重要的脚本子模块——代码filelist生成模块filelist.tcl

## 功能:

本模块用filelist.tcl脚本实现,遍历目标文件下的所有文件,并将扩展名(.v)符合要求的文件完整路径输出到指定的文档,最终形成DC读取verilog代码的约束,写入script.tcl中。

➤ 重要的脚本子模块——代码filelist生成模块filelist.tcl

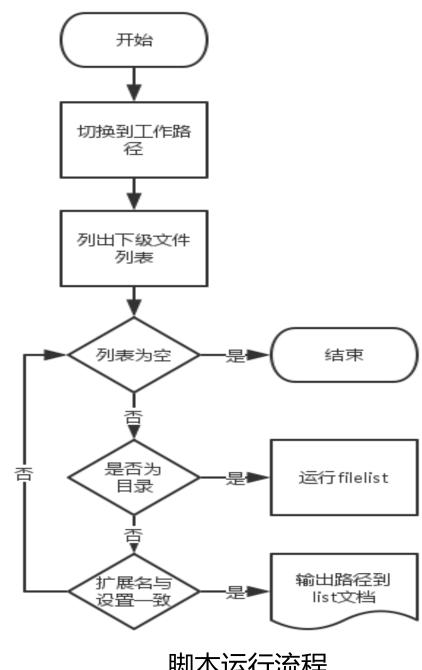

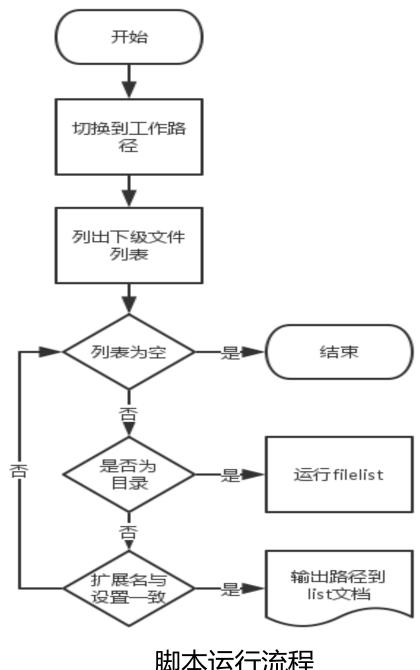

## 工作流程:

- ① 将工作路径切换到指定的工作路径

- ② 判断当前目录下的文件扩展名是否与设置的变量 extension—致,如果一致,就将该文件路径输出到指定 的文件

- ③ 如果有文件夹,则递归调用本程序,直至结束。

脚本运行流程

➤ 重要的脚本子模块——代码filelist生成模块filelist.tcl

```

proc FindFile { myDir result } {

if {[catch {cd $myDir} err]} {

puts $result $err

return}

foreach myfile [glob -nocomplain *] {

#切换到对应路径

cd $myDir

if {[string equal $myfile ""]} {

return } #如果是空文件夹就返回

set fullfile [file join $myDir $myfile]

if {[file isdirectory $myfile]} {

FindFile $fullfile $result #如果有下一级路径则递归调用本函

数

} elseif {[string equal [file extension $fullfile] [format ".%s"

$::extension]]} { #判断扩展名是否与要求一致

puts $result $fullfile}}}

```

▶ 重要的脚本子模块——时钟约束生成子模块

#### 功能和流程:

- ① 首先调用parameter.tcl脚本,读取其中用户对时钟源指定的参数,如时钟周期等;

- ② 调用find\_clk.tcl脚本,该脚本会将搜索 顶层设计中的所有的clk端口,并将所有 搜索结果输出到一个名为clk\_list的文档;

- ③ 打开clk\_list文档,将对时钟端口施加约束的指令输出到script.tcl脚本。

DC的时钟相关的约束指令

```

source [file join $::script_path test/find_clk.tcl]

#调用find clk.tcl脚本

set a [open [ille join $::script_path test/work/clk_list] r]

#打开v_list文档

set b [gets $a]

set result [open [file join $::script_path test/work/script.tcl]

a]

for {} {$b!=""} {set b [gets $a]} {

puts $result [format "create_clock -name \"clock\" -period

%u -waveform \{0 \ \%d\} \ \{ \ \%s \ \}" $::clk_source [expr

$::clk_source/2] $b]

#将生成时钟源的指令输出到script.tcl脚本

puts $result [format "set_dont_touch_network \[get_ports

%s\]" $b]

#对时钟网络设置don't touch

puts $result [format "set_drive 0 \[get_ports %s\]" $b]

#设置时钟端口驱动为无穷大

puts $result [format "set_ideal_network \[get_ports %s\]"

$b]

#设置时钟端为理想网线

close $result

```

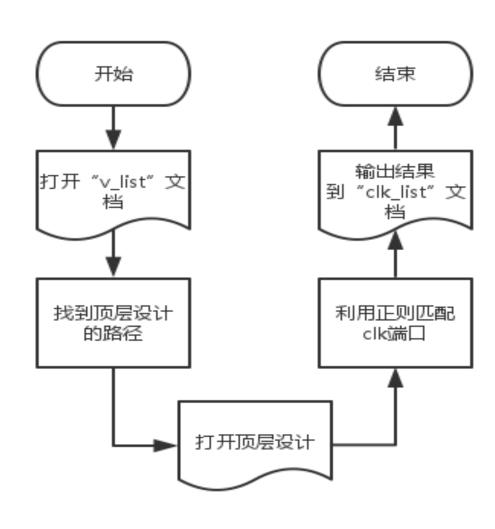

▶ 重要的脚本子模块——匹配时钟端口子模块find\_clk.tcl

## 功能:

搜索代码中的所有的时钟端口,将结果到work文件夹下的

clk\_list文档

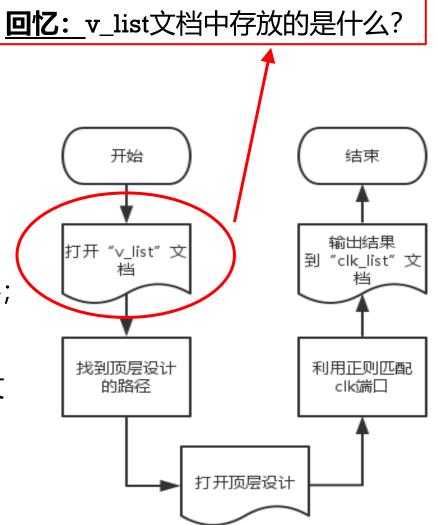

## 工作流程:

- ① 打开v\_list文档,在其中找到顶层设计的路径,并打开改设计文件;

- ② 利用正则表达式匹配其中的clk端口;

- ③ 并将匹配到的时钟端口的端口名输出到work文件夹下的clk\_list文档。

脚本运行流程

```

for {} {[eof $designfile]==0} {set fdesign [gets $designfile]} {

if {[regexp {input.*} $fdesign a]} {

#利用正则表达式匹配到声明输入端口那一行

if {[regexp {[^ ,( ]*clk[^ ,;]*} $a rport]} {

#利用正则表达式在那一行匹配后缀为clk的端口

puts $fport $rport

#将匹配到的端口名输出到clk_list文档

```

脚本运行流程

- ◆ 其余脚本工作机制类似。

- ◆ 最终,所有的约束都被写入了script.tcl中。

- ◆ script.tcl脚本完全由自动化电路综合平台生成, 并非人工编写;

- ◆ 在自动化电路综合平台运行后,由顶层脚本调用各子模块脚本生成该脚本。生成该脚本后,由顶层脚本调用该脚本,由此实现对设计的综合。

## 参考书目

- Using Tcl with Synopsys Tools. Version B-2008.09, March 2011. Synopsys.

- 集成电路静态时序分析与建模. 刘峰, 机械工业出版社.出版时间: 2016-07-01.

# 谢谢聆听!

个人教学工作主页https://customizablecomputinglab.github.io/