西南交通大学邸志雄老师主页

志之所趋,无远弗届,穷山距海,不能限也.

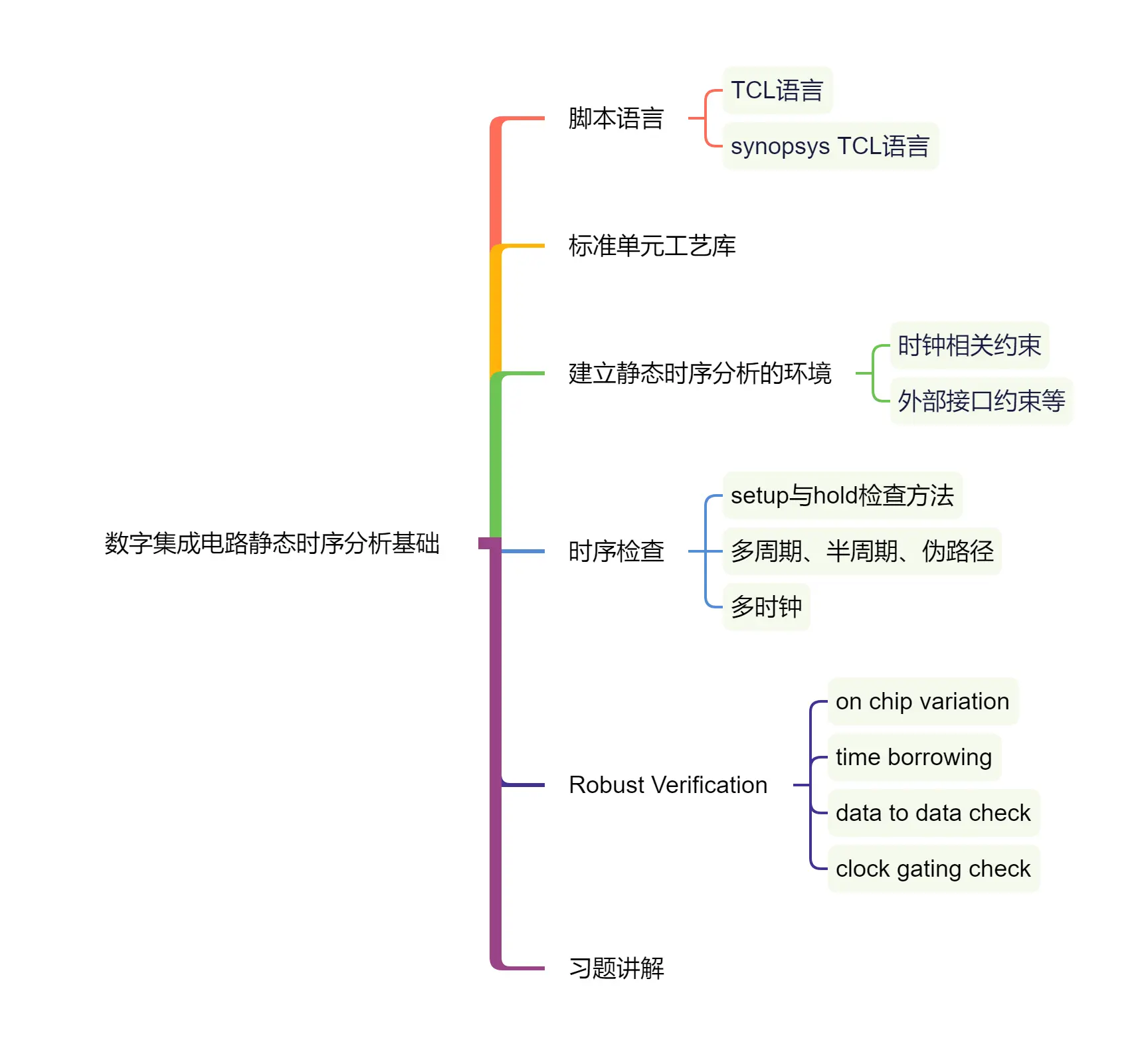

数字集成电路静态时序分析基础

课程概述

时序收敛是数字集成电路和FPGA都极为关注的指标,不管在前端RTL设计还是后端物理实现阶段都需要投入大量的时间和精力。本课程以经典书籍《Static Timing Analysis for Nanometer Designs: A Practical Approach》为教材,重点以Synopsys TCL语言入门、工艺库、复杂时序路径分析方法为核心内容,辅以时序分析笔试题,期望通过这门课程掌握静态时序分析方法。

课程大纲

- 课程概述 slide

- 脚本语言

- STA基本概念 slide

- 标准单元工艺库 slide

- 建立静态时序分析的环境 slide

- 时钟相关约束

- 外部接口约束等

- 时序检查

- Robust Verification

- 习题讲解 slide

前序知识 ---具备数字集成电路、ASIC/SoC/FPGA设计等基础知识。

基于SYNOPSYS DC 约束自动化生成框架和TCL脚本代码

- 说明文档和脚本源代码 scripts

参考资料

- Static Timing Analysis for Nanometer Designs: A Practical Approach. J. Bhasker, Rakesh Chadha. Springer Science Business Media, LLC 2009.

- 集成电路静态时序分析与建模. 刘峰, 机械工业出版社.出版时间:2016-07-01.

- 同学们也可以参考上海交通大学硕士生赵俊军对文献1的翻译工作。文章链接为(https://www.zhihu.com/people/zhao-jun-jun-19/posts)

在此非常感谢赵俊军同学的辛苦工作,他自发利用学习和科研空余时间来翻译了这本经典著作,如果感兴趣,请多关注他的知乎,为他点赞。