西南交通大学邸志雄老师主页

志之所趋,无远弗届,穷山距海,不能限也.

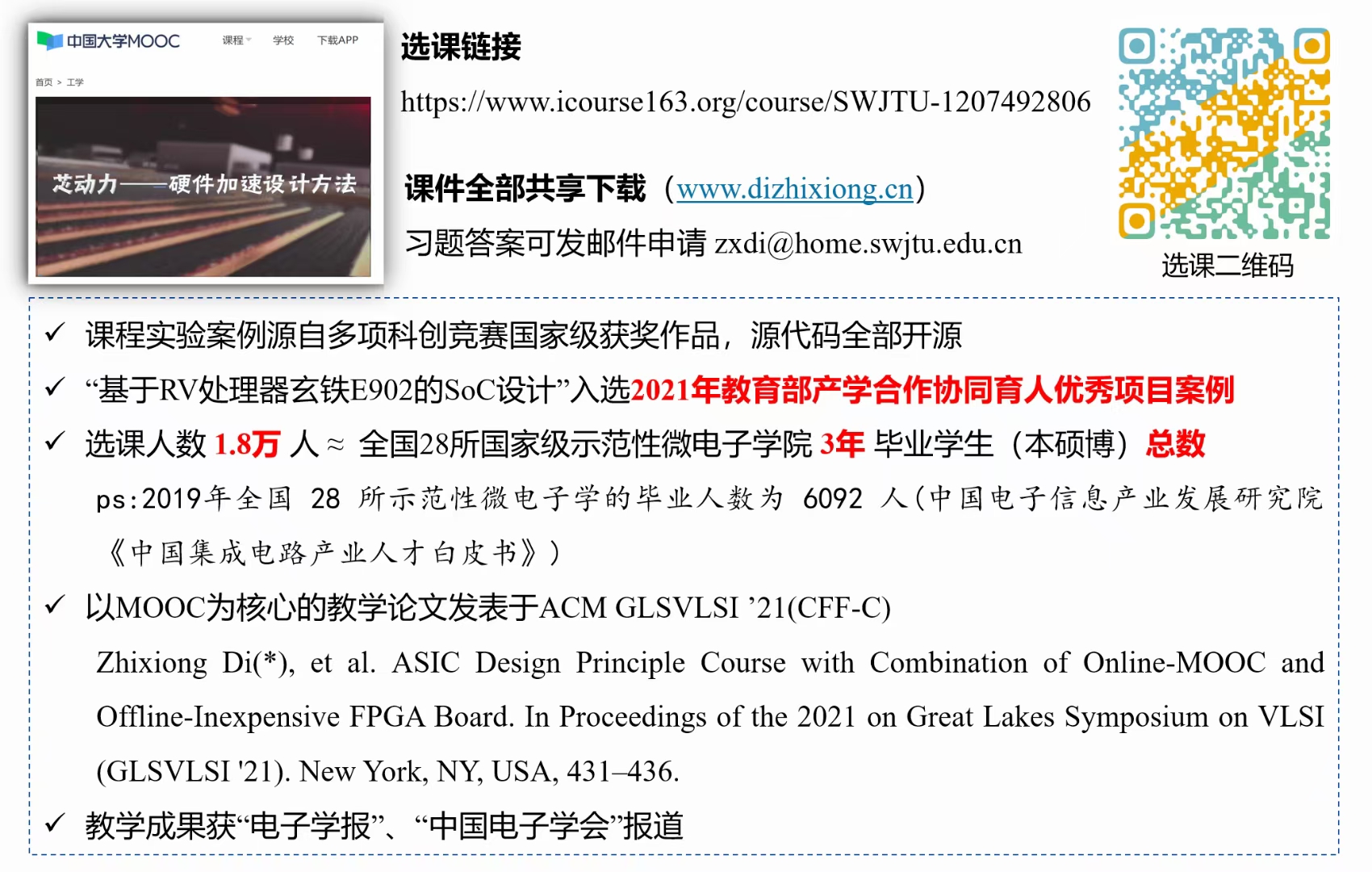

芯动力——硬件加速设计方法

- 中国大学MOOC平台,免费注册学习!练习、作业、考试题请见“中国大学MOOC”。

- 教师可以联系邮箱zxdi@home.swjtu.edu.cn获取课程所有作业参考答案。

- 如果VerilogHDL基础较薄弱,建议课前在B站学习《从电路设计的角度入门VerilogHDL》请戳此链接观看。

课程概述

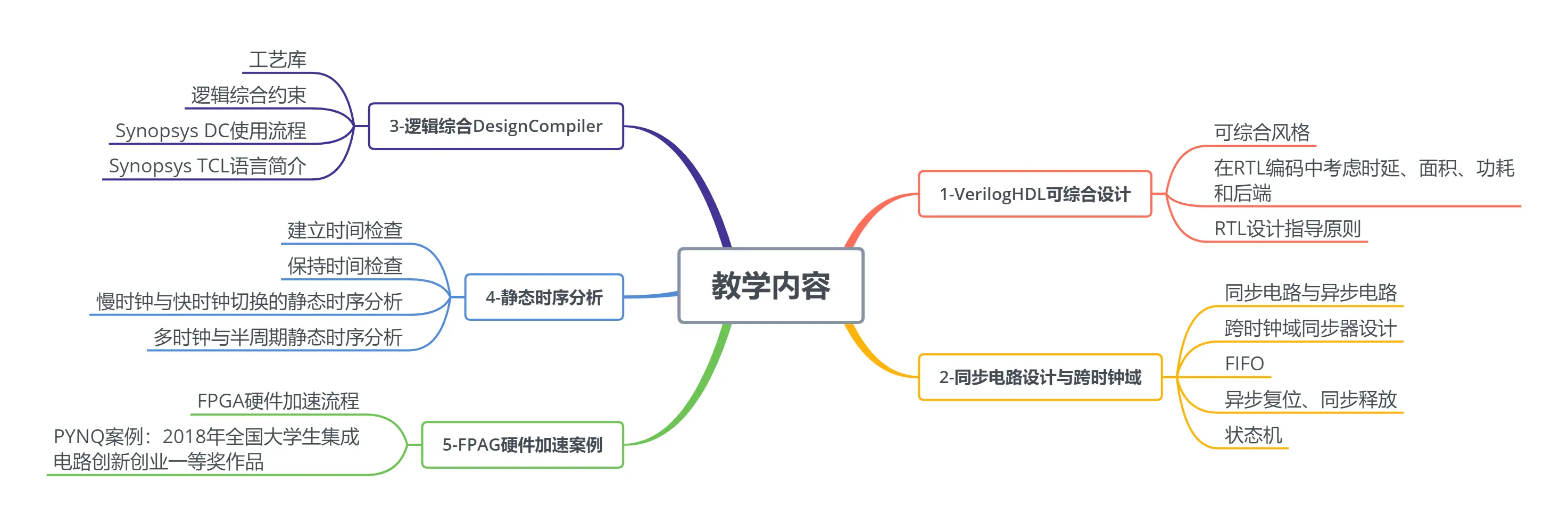

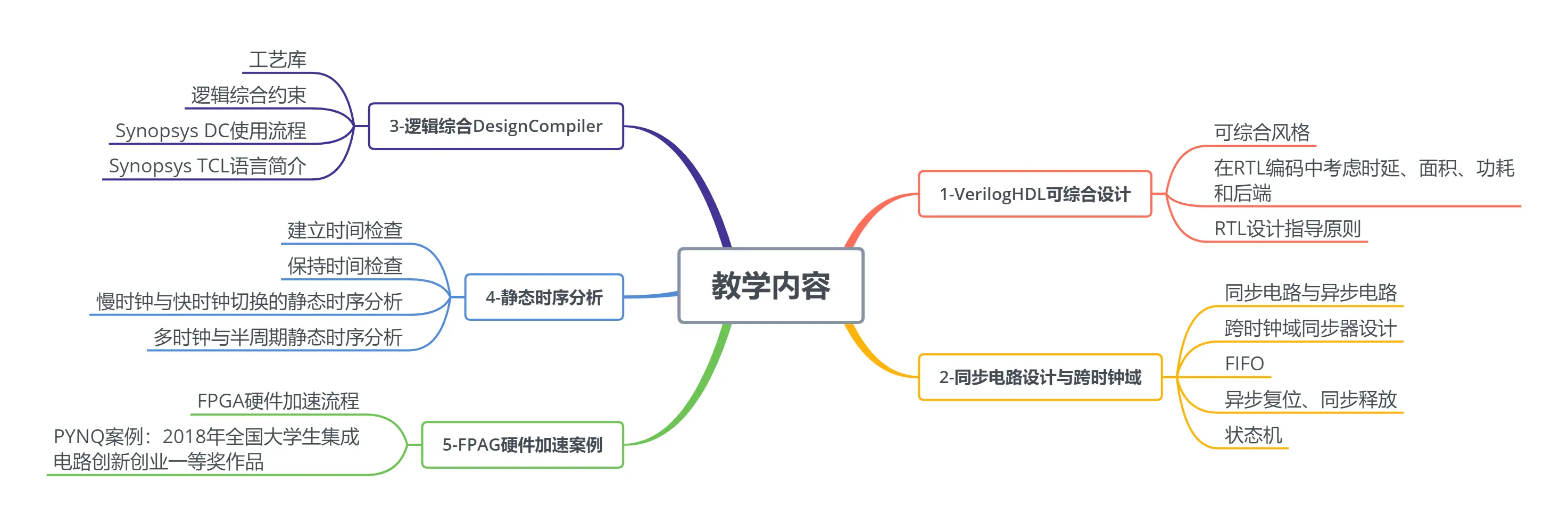

本课程的教学内容主要包括:

-

VerilogHDL可综合设计。课程收获:如何避免常见的VerilogHDL代码误区,如何在考 虑性能、面积、功耗、后端实现的情况下,编写高质量代码。

-

同步电路设计与跨时钟域电路设计。课程收获:学会理解经典跨时钟域同步电路设计 原理;理解和掌握异步FIFO"空""满"设计原理,掌握FIFO深度计算方法;理解"异步复 位、同步释放"的原理和方法;理解 "一段式"、"两段式"、"三段式"状态机电路结构 的异同,掌握状态机编写方法。

-

逻辑综合DesignCompiler基本原理和方法。课程收获:掌握DesignCompiler使用流程, 并理解DesignCompiler的约束;掌握Synopsys TCL语言的应用方法。

-

静态时序分析。课程收获:理解建立时间与保持时间的计算原理,掌握多时钟下数据 路径的建立时间和保持时间的检查方法。

-

FPGA硬件加速案例等。"FPGA硬件加速案例"采用了2018年全国大学生集成电路创新创 业一等奖作品"基于Xilinx PYNQ FPGA的Softmax函数硬件加速设计",相关工程和代码 已经在github开源。如果听众手里有PYNQ Z2开发板,则可以复现该作品。

课程大纲(附每章节slide文件)

学习目标:了解硬件加速的意义;知悉芯片设计领域的行业分工与特点;熟悉数字芯片设计的流程和EDA工具;

学习目标:知悉如何避免常见的VerilogHDL代码误区;掌握如何在考虑性能、面积、功耗、后端实现的情况下,编写高质量代码;掌握常见的RTL设计指导原则。

该章节课时标题:

学习目标:学会理解经典跨时钟域同步电路设计原理;理解和掌握异步FIFO"空""满"设计原理,掌握FIFO深度计算方法;理解"异步复位、同步释放"的原理和方法;理解 "一段式"、"两段式"、"三段式"状态机电路结构的异同,掌握状态机编写方法。

该章节课时标题:

-

3.1. 亚稳态 slide

-

3.2. 单bit信号的跨时钟域传输电路;FIFO导言 slide

-

3.3. FIFO-空满信号生成机制与深度设计方法 slide

-

3.4. FIFO知识点总结 slide

-

3.5. 同步复位异步释放电路设计 slide

-

3.6. 状态机概述与分类 slide

-

3.7. 两段式与三段式状态机的电路设计结构与分析 slide

学习目标:掌握DesignCompiler使用流程,并理解DesignCompiler的约束;掌握Synopsys TCL语言的应用方法。

该章节课时标题:

-

4.1. 逻辑综合概述与基本知识 slide

-

4.2. 标准单元工艺库 slide

-

4.3. 逻辑综合中如何施加环境约束 slide

-

4.4. 逻辑综合设计约束 slide

-

4.5. 逻辑综合中优化电路常用方法 slide

-

4.6. Synopsys TCL语言简介 slide

学习目标:理解建立时间与保持时间的计算原理,掌握多时钟下数据路径的建立时间和保持时间的检查方法。

该章节课时标题:

-

5.1. 静态时序分析入门 slide

-

5.2. 静态时序分析工具如何检查时序路径的建立时间 slide

-

5.3. 保持时间检查 slide

-

5.4. 慢时钟与快时钟切换的静态时序分析 slide

-

5.5. 多时钟与半周期静态时序分析 slide

学习目标:FPGA硬件加速案例-人工智能算法中softmax函数的硬件加速设计。基于给出的"FPGA硬件加速案例"的开源代码,理解并复现该作品。相关工程和代码已经在github开源。

课内设计: Open Mini Bitcoin Miner slide

课程图片:

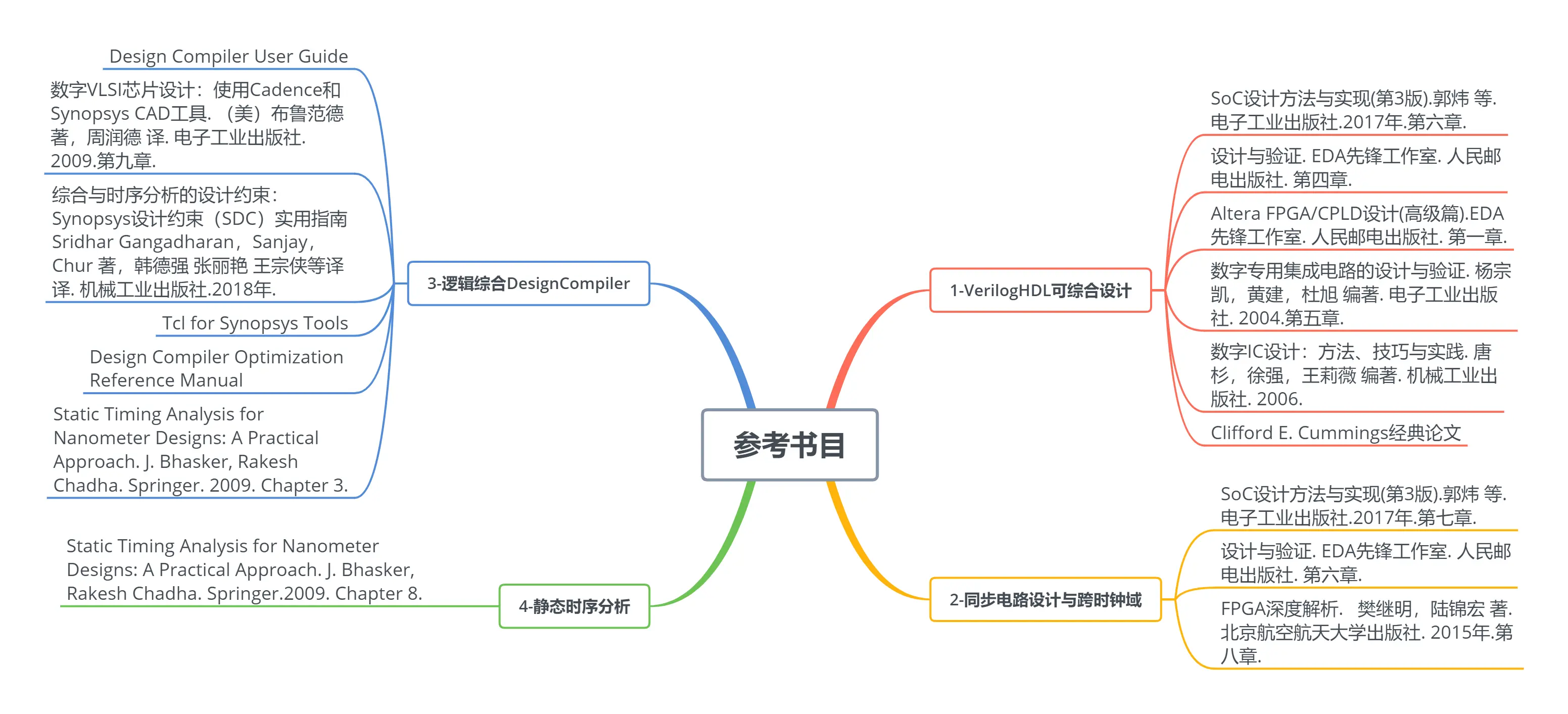

参考资料

-

SoC设计方法与实现(第3版).郭炜 等. 电子工业出版社.2017年.第六章.

-

设计与验证. EDA先锋工作室. 人民邮电出版社. 第四章.

-

Altera FPGA/CPLD设计(高级篇).EDA先锋工作室. 人民邮电出版社. 第一章.

-

数字专用集成电路的设计与验证. 杨宗凯,黄建,杜旭 编著. 电子工业出版社. 2004.第五章.

-

数字IC设计:方法、技巧与实践. 唐杉,徐强,王莉薇 编著. 机械工业出版社. 2006.

-

Clifford E. Cummings经典论文

-

SoC设计方法与实现(第3版).郭炜 等. 电子工业出版社.2017年.第七章.

-

设计与验证. EDA先锋工作室. 人民邮电出版社. 第六章.

-

FPGA深度解析. 樊继明,陆锦宏 著. 北京航空航天大学出版社. 2015年.第八章.

-

Design Compiler User Guide

-

数字VLSI芯片设计:使用Cadence和Synopsys CAD工具. (美)布鲁范德 著,周润德 译. 电子工业出版社. 2009.第九章.

-

综合与时序分析的设计约束:Synopsys设计约束(SDC)实用指南

-

Sridhar Gangadharan,Sanjay,Chur 著,韩德强 张丽艳 王宗侠等译 译. 机械工业出版社.2018年.

-

Tcl for Synopsys Tools

-

Design Compiler Optimization Reference Manual

-

Static Timing Analysis for Nanometer Designs: A Practical Approach. J. Bhasker, Rakesh Chadha. Springer. 2009. Chapter 3.

- Static Timing Analysis for Nanometer Designs: A Practical Approach. J. Bhasker, Rakesh Chadha. Springer.2009. Chapter 8.

课程内容

作业答案与解析

练习题

20分钟RTL快速练习题

RTL TEST1

RTL TEST2

RTL TEST3

RTL TEST4

RTL TEST5: Dual_SRAM_RTL

RTL TEST6: Matrix_MAC_RTL

RTL TEST7

RTL TEST8